# CHIP MULTIPROCESSORS WITH ON-CHIP AGGREGATE FUNCTION

# NETWORK

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Soohong P. Kim

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

August 2009

Purdue University

West Lafayette, Indiana

dedication...

# ACKNOWLEDGMENTS

To be added...

# TABLE OF CONTENTS

|                |                                                       |          |                                                             | Page |

|----------------|-------------------------------------------------------|----------|-------------------------------------------------------------|------|

| LIST OF TABLES |                                                       |          | vii                                                         |      |

| LI             | ST O                                                  | F FIG    | URES                                                        | viii |

| A]             | BBRI                                                  | EVIATI   | ONS                                                         | х    |

| G              | LOSS                                                  | ARY .    |                                                             | xi   |

| A]             | BSTR                                                  | ACT      |                                                             | xii  |

| 1              | Introduction                                          |          |                                                             | 1    |

|                | 1.1                                                   | Motiv    | ation                                                       | 1    |

|                | 1.2                                                   | Our A    | Approach                                                    | 2    |

|                | 1.3                                                   | Relate   | ed Work                                                     | 4    |

|                |                                                       | 1.3.1    | Dedicated Hardware for Barriers and Collectives             | 4    |

|                |                                                       | 1.3.2    | Other Hardware Support for Barriers                         | 4    |

|                |                                                       | 1.3.3    | Off-chip Aggregate Function Network for COW                 | 5    |

|                |                                                       | 1.3.4    | Operand Networks                                            | 5    |

|                |                                                       | 1.3.5    | MIMD ISA Extensions                                         | 5    |

|                | 1.4                                                   | Contr    | ibutions                                                    | 6    |

|                | 1.5                                                   | Organ    | nization of this Dissertation                               | 6    |

| 2              | Para                                                  | allel Co | mmunication Models                                          | 7    |

|                | 2.1                                                   | Share    | d Memory Communication Model                                | 7    |

|                | 2.2                                                   | Messa    | ge Passing Communication Model                              | 11   |

|                | 2.3                                                   | Synch    | ronous Aggregate Communication Model                        | 14   |

| 3              | On-                                                   | Chip Sy  | unchronous Aggregate Communication Model and ISA Extensions | 18   |

|                | 3.1 On-Chip Synchronous Aggregate Communication Model |          | hip Synchronous Aggregate Communication Model               | 18   |

|                |                                                       | 3.1.1    | Overview                                                    | 18   |

|                |                                                       | 3.1.2    | Thread Migration Support                                    | 20   |

# Page

|   |      | 3.1.3   | Blocking vs. Busy-waiting AFN $OP$ RD Instructions           | 20 |

|---|------|---------|--------------------------------------------------------------|----|

|   |      | 3.1.4   | Security                                                     | 22 |

|   |      | 3.1.5   | Comparison                                                   | 23 |

|   | 3.2  | ISA E   | xtensions for the On-Chip AFN                                | 24 |

|   |      | 3.2.1   | AFN Programming Environment                                  | 24 |

|   |      | 3.2.2   | AFN Instructions                                             | 24 |

| 4 | On-0 | Chip Al | FN Architecture                                              | 27 |

|   | 4.1  | Baseli  | ne CMP-AFN Architecture                                      | 27 |

|   | 4.2  | AFU-0   | core Interconnect                                            | 27 |

|   | 4.3  | Aggre   | gate Function Unit                                           | 29 |

|   |      | 4.3.1   | AFU Tables                                                   | 30 |

|   |      | 4.3.2   | AFU State Machines                                           | 30 |

|   |      | 4.3.3   | Aggregate Function ALUs                                      | 31 |

|   |      | 4.3.4   | AFU Allocation Table                                         | 33 |

|   | 4.4  | A Cas   | e for CMP-AFN                                                | 33 |

|   |      | 4.4.1   | Barrier Synchronization Latency for CMP-AFN                  | 33 |

|   |      | 4.4.2   | Barrier Synchronization Latency in a conventional CMP $$     | 35 |

| 5 | Eval | uation  | Methodology and Results                                      | 38 |

|   | 5.1  | Simula  | ation Target Configurations                                  | 38 |

|   | 5.2  | Re-tar  | geting OpenMP Benchmarks for CMP-AFN                         | 40 |

|   |      | 5.2.1   | barrier Construct                                            | 42 |

|   |      | 5.2.2   | critical Construct                                           | 43 |

|   |      | 5.2.3   | OpenMP Locks                                                 | 43 |

|   | 5.3  | _       | iling OpenMP Benchmarks for CMP Simics Targets: Check-<br>ng | 44 |

|   | 5.4  | Overv   | iew of OpenMP Benchmarks                                     | 46 |

|   | 5.5  | EPCC    | Microbenchmark                                               | 48 |

|   |      | 5.5.1   | syncbench.c: testbar() for barrier synchronization $\ldots$  | 49 |

vi

|    |      | 5.5.2                                      | syncbench.c: testlock() for OpenMP locks                  | 49  |

|----|------|--------------------------------------------|-----------------------------------------------------------|-----|

|    |      | 5.5.3                                      | syncbench.c: testred() for reduction                      | 51  |

|    | 5.6  | SPEC                                       | OMP2001 Benchmark Suite                                   | 51  |

|    |      | 5.6.1                                      | 316.applu_m                                               | 57  |

|    |      | 5.6.2                                      | 320.equake_m                                              | 57  |

|    |      | 5.6.3                                      | 324.apsi_m                                                | 57  |

|    |      | 5.6.4                                      | 330.art_m                                                 | 57  |

|    |      | 5.6.5                                      | 332.ammp_m                                                | 58  |

|    | 5.7  | Perfor                                     | mance Evaluation                                          | 58  |

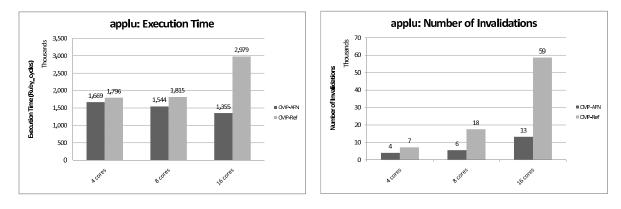

|    |      | 5.7.1                                      | Performance Evaluation of 316.applu_m                     | 61  |

| 6  | Sum  | mary                                       |                                                           | 68  |

|    | 6.1  | Conclu                                     | usions                                                    | 68  |

|    | 6.2  | Future                                     | e Work                                                    | 69  |

| LI | ST O | F REF                                      | ERENCES                                                   | 70  |

| А  | AFN  | FN Extensions to IA-32                     |                                                           |     |

|    | A.1  | Overview of ISA Extensions for on-chip AFN |                                                           |     |

|    | A.2  | .2 AFN Programming Environment             |                                                           |     |

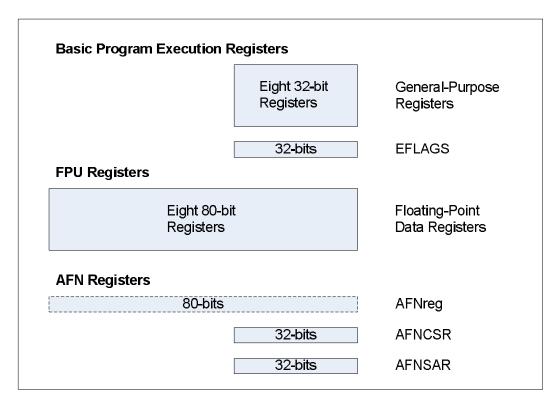

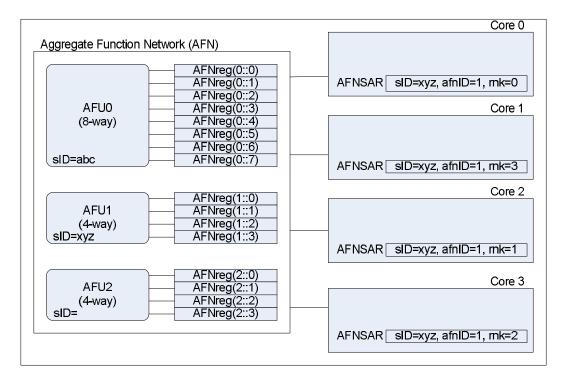

|    |      | A.2.1                                      | AFU                                                       | 77  |

|    |      | A.2.2                                      | AFNreg Registers                                          | 78  |

|    |      | A.2.3                                      | AFNSAR Register                                           | 78  |

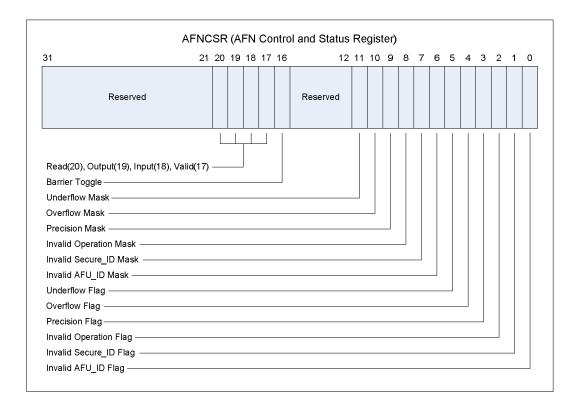

|    |      | A.2.4                                      | AFNCSR Control and Status Register                        | 80  |

|    | A.3  | AFN I                                      | Instructions                                              | 82  |

|    |      | A.3.1                                      | Opcodes                                                   | 83  |

|    |      | A.3.2                                      | Instruction Format                                        | 83  |

|    |      | A.3.3                                      | Opcode Column in the Instruction Summary Table $\ldots$ . | 83  |

|    |      | A.3.4                                      | Instruction Column in the Instruction Summary Table       | 85  |

| VI | TA   |                                            |                                                           | 104 |

# LIST OF TABLES

| Table |                                                                                                                                                                                                                                                                       | Page |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.1   | AFN Instructions by Group                                                                                                                                                                                                                                             | 25   |

| 4.1   | Packets to communicate between CPU cores and on-chip AFN                                                                                                                                                                                                              | 29   |

| 4.2   | A Case for CMP-AFN                                                                                                                                                                                                                                                    | 34   |

| 4.3   | GOMP latencies                                                                                                                                                                                                                                                        | 35   |

| 4.4   | barr sync latency comparison                                                                                                                                                                                                                                          | 36   |

| 5.1   | Configurations for Simulated Targets                                                                                                                                                                                                                                  | 41   |

| 5.2   | Replacing OpenMP constructs with AFN Library routines                                                                                                                                                                                                                 | 42   |

| 5.3   | Static Counts of OpenMP Constructs and Run-Time Routines in SPEC OMP Benchmarks for Evaluation                                                                                                                                                                        | 48   |

| 5.4   | OpenMP constructs used in SPEC OMPM2001 benchmark suite: BARR<br>indicates for BARRIER construct, CRIT for CRITICAL construct, LOCK for<br>OpenMP locks, RED for REDUCTION clause, and i.barr for implicit barrier<br>synchronization. The numbers are static counts. |      |

| 5.5   | SPEC OMPM2001 Benchmark Suite Description                                                                                                                                                                                                                             | 55   |

|       |                                                                                                                                                                                                                                                                       |      |

# LIST OF FIGURES

| Figu | Ire                                                                                                                                                                                                                                                                             | Page |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1  | A generic CMP-AFN architecture: The on-chip AFN consists of AFU (aggregate function unit) and AFU-core Interconnect.                                                                                                                                                            | 3    |

| 2.1  | pi: a sample algorithm that computes the value of Pi $[30]$                                                                                                                                                                                                                     | 8    |

| 2.2  | An OpenMP version of pi                                                                                                                                                                                                                                                         | 10   |

| 2.3  | An MPI version of pi [30]                                                                                                                                                                                                                                                       | 12   |

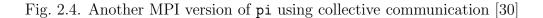

| 2.4  | Another MPI version of pi using collective communication $[30]$                                                                                                                                                                                                                 | 13   |

| 2.5  | Differences between the message-passing communication model (shown on the left) and the synchronous aggregate communication model                                                                                                                                               | 15   |

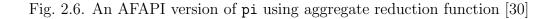

| 2.6  | An AFAPI version of pi using aggregate reduction function $[30]$                                                                                                                                                                                                                | 16   |

| 2.7  | A UPC version of pi.c                                                                                                                                                                                                                                                           | 17   |

| 3.1  | AFN Checkout Instruction with Blocking                                                                                                                                                                                                                                          | 21   |

| 3.2  | AFN Checkout Instruction with Busy-Waiting                                                                                                                                                                                                                                      | 22   |

| 3.3  | Differences Between Cache-Coherent Shared Memory CMP without and with the on-chip AFN                                                                                                                                                                                           | 23   |

| 4.1  | A Baseline CMP architecture with on-chip AFN, similar to Larrabee, where the ring network is the interprocessor network that connects multiple cores and L2 cache banks. The number of cores and L2 cache banks are implementation-dependent. (Adapted from Seiler et. al 2008) | 27   |

| 4.2  | On-Chip AFN Architecture: On-chip AFN consists of AFU and AFU-core<br>Interconnect.                                                                                                                                                                                             | 28   |

| 4.3  | State Machine for Barrier Synchronization (AFNBARR/AFNBARRRD)                                                                                                                                                                                                                   | 31   |

| 4.4  | State Machine for Reduction Operation (AFNOP/AFNOPRD)                                                                                                                                                                                                                           | 32   |

| 4.5  | gomp_barrier_wait() when all four threads arrived a barrier at the same time                                                                                                                                                                                                    | 37   |

| 5.1  | A four-core CMP-AFN Simics Target                                                                                                                                                                                                                                               | 39   |

| 5.2  | Steps to create executables for CMP-AFN and CMP-REF targets                                                                                                                                                                                                                     | 45   |

| Figure |                                                                                                         |    |

|--------|---------------------------------------------------------------------------------------------------------|----|

| 5.3    | Structure of a Program with magic instructions                                                          | 47 |

| 5.4    | delay(): EPCC microbenchmark                                                                            | 49 |

| 5.5    | testbar(): EPCC microbenchmark for barrier synchronization                                              | 50 |

| 5.6    | testlock(): EPCC microbenchmark for OpenMP Lock. OUTERREPS=1 innerreps=128, and delaylength=500.        |    |

| 5.7    | testred(): EPCC microbenchmark for reduction                                                            | 53 |

| 5.8    | ssor.f from SPEC OMP 316.applu_m                                                                        | 56 |

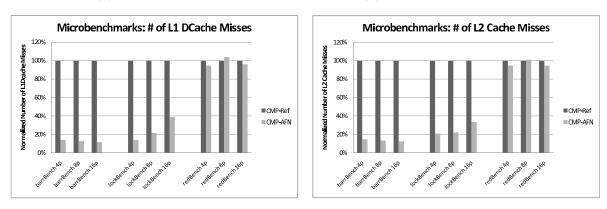

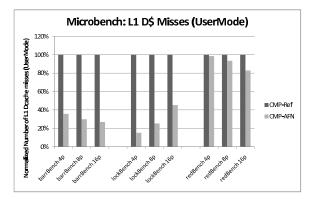

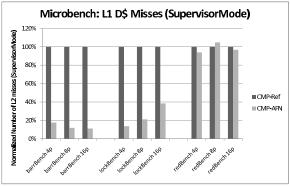

| 5.9    | Summary of EPCC OpenMP Microbenchmark Results                                                           | 59 |

| 5.10   | Summary of SPEC OMP Benchmark Results                                                                   | 60 |

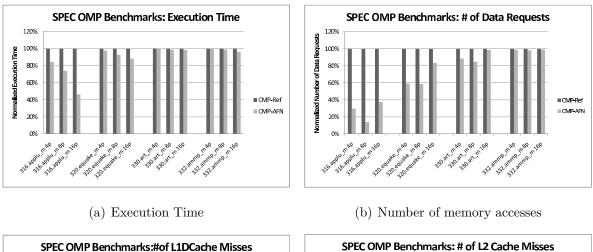

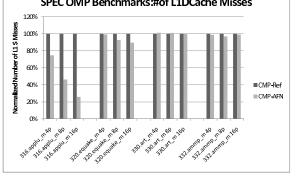

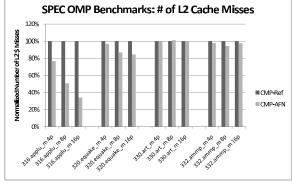

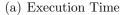

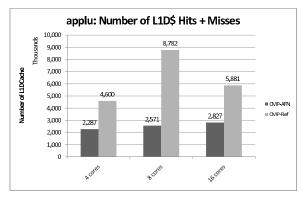

| 5.11   | SPEC OMP 316.applu_m                                                                                    | 61 |

| 5.12   | SPEC OMP 316.applu_m (continued)                                                                        | 62 |

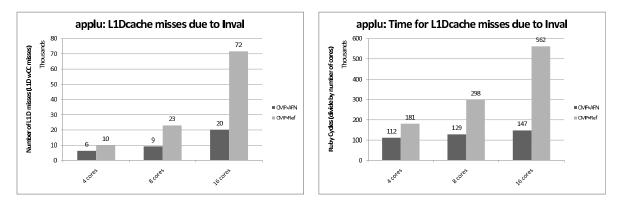

| 5.13   | SPEC OMP 316.applu_m (continued)                                                                        | 63 |

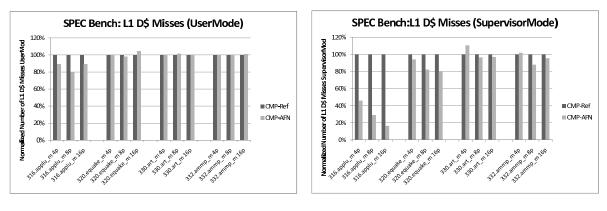

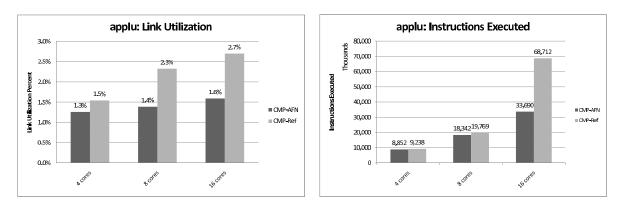

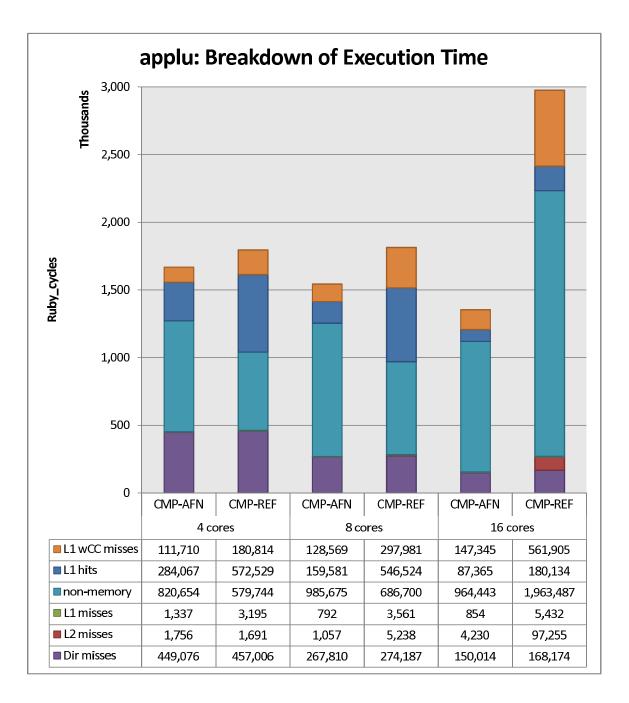

| 5.14   | applu: Breakdown of Execution Time by Cache Misses                                                      | 65 |

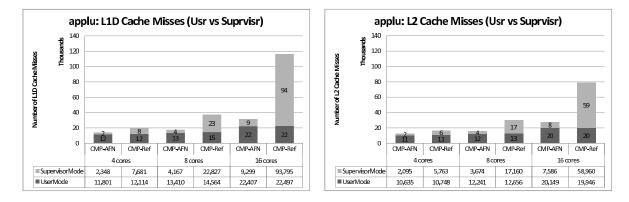

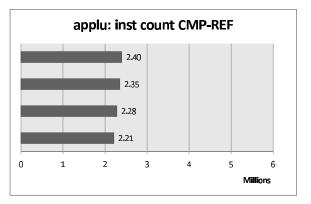

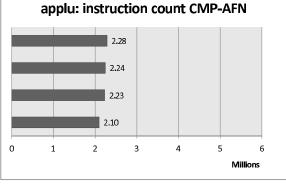

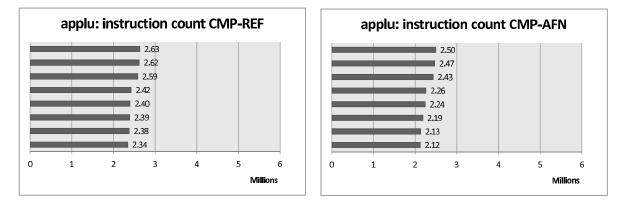

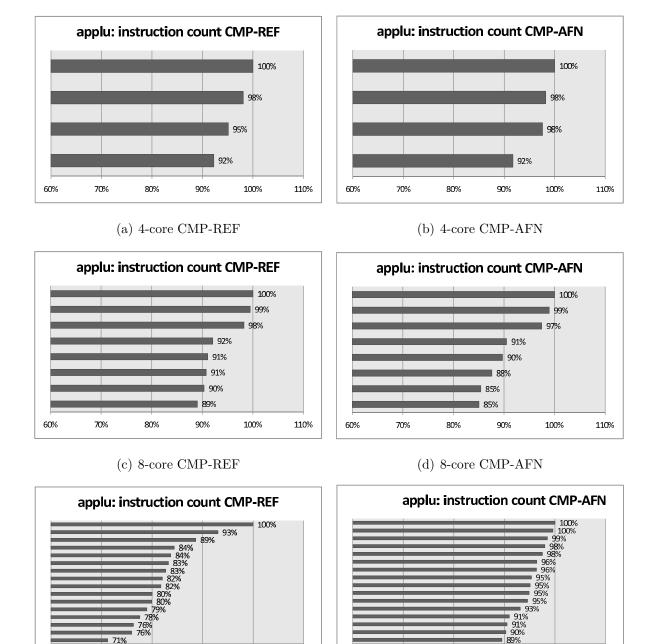

| 5.15   | applu: Instruction Count Distribution Across Cores                                                      | 66 |

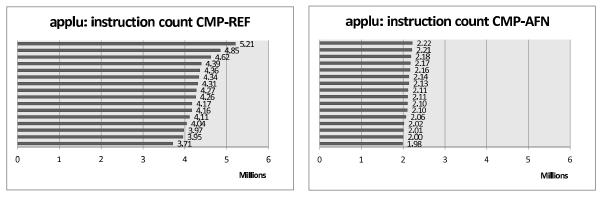

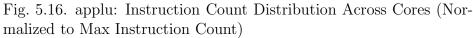

| 5.16   | applu: Instruction Count Distribution Across Cores (Normalized to Max<br>Instruction Count)             | 67 |

| A.1    | AFN Programming Environment: a single thread's perspective                                              | 75 |

| A.2    | AFNregs and AFUs                                                                                        | 77 |

| A.3    | AFNCSR Control/Status Register                                                                          | 79 |

| A.4    | AFNCSR register bit positions                                                                           | 81 |

| A.5    | An Example Opcode Summary Table: consists of three columns – "Opcode", "Instruction", and "Description" | 84 |

# ABBREVIATIONS

- AFAPI Aggregate Function API Application Programming Interface

- AFN Aggregate Function Network

- AFU Aggregate Function Unit

- CMP Chip Multiprocessor

# GLOSSARY

GOMP An OpenMP implementation for GCC (GNU Compiler Collection). GCC version 4.2 and later.

Simics host Refers to the computer on which one is running Simics.

Simics target Refers to the computer simulated by Simics.

#### ABSTRACT

Kim, Soohong P. Ph.D., Purdue University, August, 2009. Chip Multiprocessors with On-Chip Aggregate Function Network. Major Professors: Samuel P. Midkiff and Henry G. Dietz.

State-of-the-art on-chip networks and block-based cache coherence protocols used in cache-coherent shared-memory Chip MultiProcessors (CMPs) are inefficient for collective operations across cores. Performance of CMPs can be seriously degraded by the multitude of memory requests and coherence messages required to implement each collective operation. This thesis presents a CMP-AFN architecture and Instruction Set Architecture (ISA) extensions that augment a conventional shared-memory CMP with a tightly-integrated Aggregate Function Network (AFN) that implements low-latency collective operations without using or interfering with the memory hierarchy. For a modest increase in circuit complexity, traffic within a CMP's internal network is dramatically reduced, improving the performance of caches and reducing power consumption. Full system simulations of 16-core CMPs show a CMP-AFN outperforms the reference design significantly, eliminating up to 52% of memory accesses and up to 73% of private L1 data cache misses in both the EPCC OpenMP microbenchmarks and SPEC OMP benchmarks.

## 1. INTRODUCTION

#### 1.1 Motivation

Chip Multiprocessors (CMPs) dominate the important desktop, server and HPF market segments because they allow faster application performance using shared memory programming models. Application studies show, however, that synchronization overhead is the performance bottleneck in parallel applications for cache-coherent shared memory multiprocessors [6–8]. Synchronization operations often account for significant fractions of execution time and can both limit the scalability of parallel programs on very large machines and negatively affect the ability of large-scale systems to exploit fine-grain parallelism. Sampson, et al. [9] shows the importance of fast barrier synchronization in shared-memory many-core CMPs as a prerequisite for the exploitation of fine-grained parallelism.

Despite enabling lower latency for interprocessor communication, current state-ofthe-art on-chip networks and block-based cache coherence protocols for shared memory multi-core architectures are inefficient for collective communication [10]. Multiple memory requests and coherence messages must be transmitted among CPU cores and cache controllers to implement a single collective operation. Software synchronization primitives include atomic read-modify-write (RMW) instructions, which are on the critical path of the synchronization algorithm. When these instructions are implemented with shared variables, they interfere with the cache coherence protocol and generate a significant amount of network traffic because of contention for synchronization flags. Coherency-related overheads are not the only ones suffered. Aslot, et al. [6] shows that there are two aspects of lock overhead: the overhead of executing extra instructions while spin waiting and the overhead of acquiring the lock. For scalable CMP performance, the negative impact of both aspects must be reduced or eliminated.

#### 1.2 Our Approach

The solution we propose is the adoption and adaptation of the synchronous aggregate communication model [11], which was initially developed for the cluster of workstations (COW). The synchronous aggregate communication model can be implemented within a CMP with the on-chip Aggregate Function Network (AFN) and ISA extensions. In this dissertation, we detail the new CMP-AFN architecture and the corresponding instruction set architecture (ISA) extensions that augment a shared memory chip multiprocessor with an aggregate function network and an interface between CPU cores and the on-chip AFN.

In the CMP-AFN architecture (shown in Figure 1.1), collective communication is performed without using or interfering with the on-chip cache coherent shared memory hierarchy. Collective communication can be performed via on-chip AFN, a dedicated network or an embedded virtual network in an existing on-chip interconnect. Because spin-wait on the shared variables for the synchronization primitives can be avoided in the CMP-AFN, the excessive coherence messages are eliminated in the on-chip interconnect and CPU time waste can be avoided. As a result, CMP-AFN provides low latency collective operations and reduces coherence traffic, resulting in effective use of on-chip cache and low power consumption.

The goal of our research is to explore the synchronous aggregate communication model in cache-coherent shared-memory chip multiprocessors to exploit multithreaded applications. We focus primarily on the parallel execution model associated with OpenMP, but our approach is applicable to any shared-memory programming model that supports barriers and collective operations such as reduction.

Fig. 1.1. A generic CMP-AFN architecture: The on-chip AFN consists of *AFU* (aggregate function unit) and *AFU-core Interconnect*.

#### 1.3 Related Work

We now discuss prior work related to this dissertation, organized by topic.

#### **1.3.1** Dedicated Hardware for Barriers and Collectives

The NYU Ultracomputer [12] and the IBM RP3 [13] are shared memory architectures in which the multistage interconnection networks that combine multiple messages that reference identical memory location. The Cray T3D [14] directly supports barrier synchronization, swap, and Fetch-and-Increment. The CM-5 Connection Machine [15] has a control network that supports reduction operations, prefix operations, maximum, logical OR, and XOR. Cedar [16] and Alliant FX/8 supported synchronization hardware. Tera and Denelcor HEP also supported synchronization hardware. The IBM BlueGene/L [17] has three types of networks that make up the interprocessor "fabric". In addition to a Torus interconnect for the point-to-point messages, it has a collective network for one-to-all broadcast and collective operations, and a barrier network for barrier synchronization. The proposed CMP-AFN architecture features the dedicated on-chip hardware for barrier synchronization and collective communication within a single chip multiprocessor.

#### 1.3.2 Other Hardware Support for Barriers

A barrier filter [9] is a hardware mechanism for the CMP architecture for barrier synchronization that does not rely on locks nor busy waiting. Instead, it starves processing elements' requests to cache lines until all processing elements arrive at the barrier, then fills a cache line at the synchronization point. A barrier filter does not provide an effective mechanism for collective communication. Although it does not require ISA extensions or CPU core modification, address tag filtering might be in the critical path for all memory accesses, not just barrier synchronization, and hence can potentially increase the latency for all memory accesses.

#### 1.3.3 Off-chip Aggregate Function Network for COW

PAPERS [18] is a custom network hub that is attached to a cluster of workstations (COW). This *off-chip* aggregate function network design uses a combination of barrier synchronization with a four-bit wide global NAND to construct a robust library of aggregate functions. While PAPERS is off-chip aggregate function networks for the cluster architecture, the on-chip AFN presented in this thesis is for the shared memory multi-core architectures and features the architectural support for thread migration by operating systems.

#### 1.3.4 Operand Networks

A variety of architectures have been proposed to support and utilize operand networks, including RAW [19], TRIPS [20], and WaveScalar [21]. Operand networks communicate register values between consumer and producer instructions. The onchip AFN can be considered as an operand network to communicate register values among multiple producer instructions and multiple consumer instructions for synchronous collective communication, that are performed on the network.

#### 1.3.5 MIMD ISA Extensions

There has been much research on ISA extensions to support various forms of hardware multithreading. Multiple Instruction Stream Computers (MISC) [22] is a message-passing based hardware mechanism where the parallel execution of multiple instruction streams can be orchestrated. MISC supports point-to-point communication between processing elements and between PEs and the memory subsystem. Multiple Instruction Stream Processing (MISP) architecture [23] provides inter-sequencer signaling and an asynchronous control transfer mechanism.

#### 1.4 Contributions

We make the following major contributions:

- We introduce the synchronous aggregate communication model to chip multiprocessor architectures to provide low-latency collective operations and reduced on-chip network traffic, resulting in the effective use of on-chip cache and low power consumption.

- We describe on-chip aggregate function network architecture and associated ISA extensions that implement the synchronous aggregate communication model and allow the operating system to schedule threads to one CPU core to another during the execution of a collective operation.

- We provide experimental results using full-system simulation of CMPs showing the performance benefits of the proposed techniques are large. In an 8-core CMP, we see speedups of up to 35% on the SPEC OMP benchmarks, with benefits increasing with higher core count.

#### 1.5 Organization of this Dissertation

Chapter 2 discusses various parallel communication models. Chapter 3 presents the on-chip synchronous aggregate communication model and ISA (Instruction Set Architecture) extensions for the aggregate communication model. Chapter 4 describes the on-chip AFN architecture and CMP-AFN architecture. Chapter 5 presents the evaluation methodology and experiment results. Finally, Chapter 6 provides conclusions and future work.

# 2. PARALLEL COMMUNICATION MODELS

In this chapter, we discuss various parallel communication models for multi-core architecture, i.e. shared memory communication model, point-to-point message passing communication model, and synchronous aggregate communication model.

Although we do not discuss in details, but there are more intra-socket parallel communication models for the architectures such as 80-core Intel Terascale processors [24] (point-to-point communication), IBM Cell BE-based systems [25] [26] (point-to-point combined with DMA), and PGAS (Partitioned Global Address Space) on Multi-Cores [27] [28] ("one-sided" communication, i.e. load/store on shared memory communication model).

In addition to comparison of these parallel communication model, we present a representative programming language (OpenMP, MPI, AFAPI, and UPC) and a sample program for each parallel communication discussed here. We selected a sample algorithm to compare various approaches. Shown in Figure 2.1, the algorithm computes the value of Pi and has been used in various publications [29] [30] to demonstrate a variety of different parallel programming environments.

#### 2.1 Shared Memory Communication Model

Shared Memory is a model for interactions between processing elements (PEs) within a parallel system. Shared memory systems include CMP (Chip Multi-Processors), SMP (Symmetric Multi-Processors), or DSM (Distributed Shared Memory). PEs in shared memory systems share a (either logically or physically) single memory and a value written to shared memory by one PE can be directly accessed by other PEs. Shared memory is generally considered easier to program than message passing, but

```

#include <stdlib.h>

#include <stdio.h>

main(int argc, char **argv) {

register double width, sum;

register int intervals, i;

/* get the number of intervals */

intervals = atoi(argv[1]);

width = 1.0 / intervals;

/* do the computation */

sum = 0;

for (i=0; i<intervals; ++i) {</pre>

register double x = (i + 0.5) * width;

sum += 4.0 / (1.0 + x * x);

}

sum *= width;

printf("Estimation of pi is %f\n", sum);

return(0);

}

```

Fig. 2.1. pi: a sample algorithm that computes the value of Pi [30]

it requires on-chip cache-coherence protocol, which requires very high development cost and time-to-market.

### OpenMP

OpenMP [31] [32] [33] is an industry standard set of pragmas, environment variables, and a run-time library that tell the compilers (C++ and Fortran) when, where, and how to create multithreaded code for shared memory multiprocessors. With OpenMP, programmers tell the compiler what to do with threads at an abstract level and leave the low-level details (such as thread management) to the compiler. This approach makes OpenMP much easier to use than Pthreads, but at the expense of some control and some performance. Unlike MPI, no explicit communication is used, instead inter-thread communication is done implicitly via shared memory with load-/store instructions. As it is limited to the shared memory architectures, OpenMP for non-shared memory multiprocessors have been proposed [34] [35]. Figure 2.2 shows an OpenMP version of the pi.c algorithm.

```

#include <stdlib.h>

#include <stdio.h>

#include <omp.h>

int main(int argc, char **argv) {

register double width, sum, x;

register int i, intervals;

/* get the number of intervals */

intervals = atoi(argv[1]);

width = 1.0 / (double) intervals;

/* do the local computations, followed by reduction \ast/

sum = 0;

#pragma omp parallel for reduction(+:sum) private(x)

for (i=0;i< intervals; i++){</pre>

x = (i + 0.5) * width;

sum += 4.0 / (1.0 + x * x);

}

/* have only the master thread print the result \ast/

#pragma omp master

{

/* scale by width */

sum = sum * width;

printf("Estimation of pi is %14.12lf\n", sum);

}

exit(0);

}

```

Fig. 2.2. An OpenMP version of pi

#### 2.2 Message Passing Communication Model

Message Passing is a model for interactions between processing elements (PEs) within a parallel system, typically cluster architectures. In general, a message is constructed by software on one PE and is sent through an interconnection network to another PE, which then must accept and act upon the message contents. Although the overhead in handling each message (latency) may be high, there are typically few restrictions on how much information each message may contain. Thus, message passing can yield high bandwidth making it a very effective way to transmit a large block of data from one PE to another. In the same token, this point-to-point communication model is not efficient for collective communication because it requires global communications from all PEs with relatively smaller data. On the other hand, point-to-point communication does not require the expensive hardware support for cache coherent protocol. Therefore, it is easier and faster to build the multi-core architectures that only requires point-to-point communication model.

# $\mathbf{MPI}$

The Message Passing Interface (MPI) [36] [37] is a language-independent communications API (Application Programming Interface) for message passing on cluster architectures. It expresses parallelism explicitly rather than implicitly. MPI is successful in achieving high scalability and high portability thanks to the underlying hardware architecture. However, MPI requires more programming efforts compared to OpenMP as programmers need to explicitly schedule inter-PE communication.

Figure 2.3 shows an MPI program for the pi algorithm that uses basic MPI messagepassing calls for each PE to send its partial sum to PE 0, which sums and prints the result. Figure 2.4 shows another MPI version for the pi algorithm that uses collective communication (which, for this particular application, is clearly the most appropriate).

```

#include <stdlib.h>

#include <stdio.h>

#include <mpi.h>

main(int argc, char **argv) {

register double width;

double sum, lsum;

register int intervals, i;

int nproc, iproc;

MPI_Status status;

if (MPI_Init(&argc, &argv) != MPI_SUCCESS) exit(1);

MPI_Comm_size(MPI_COMM_WORLD, &nproc);

MPI_Comm_rank(MPI_COMM_WORLD, &iproc);

intervals = atoi(argv[1]);

width = 1.0 / intervals;

lsum = 0;

for (i=iproc; i<intervals; i+=nproc) {</pre>

register double x = (i + 0.5) * width;

lsum += 4.0 / (1.0 + x * x);

}

lsum *= width;

if (iproc != 0) {

MPI_Send(&lbuf, 1, MPI_DOUBLE, 0, 0, MPI_COMM_WORLD);

} else {

sum = lsum;

for (i=1; i<nproc; ++i) {</pre>

MPI_Recv(&lbuf, 1, MPI_DOUBLE, MPI_ANY_SOURCE,

MPI_ANY_TAG, MPI_COMM_WORLD, &status);

sum += lsum;

}

printf("Estimation of pi is %f\n", sum);

}

MPI_Finalize();

return(0);

}

```

Fig. 2.3. An MPI version of pi [30]

```

#include <stdlib.h>

#include <stdio.h>

#include <mpi.h>

main(int argc, char **argv) {

register double width;

double sum, lsum;

register int intervals, i;

int nproc, iproc;

if (MPI_Init(&argc, &argv) != MPI_SUCCESS) exit(1);

MPI_Comm_size(MPI_COMM_WORLD, &nproc);

MPI_Comm_rank(MPI_COMM_WORLD, &iproc);

intervals = atoi(argv[1]);

width = 1.0 / intervals;

lsum = 0;

for (i=iproc; i<intervals; i+=nproc) {</pre>

register double x = (i + 0.5) * width;

lsum += 4.0 / (1.0 + x * x);

}

lsum *= width;

MPI_Reduce(&lsum, &sum, 1, MPI_DOUBLE,

MPI_SUM, 0, MPI_COMM_WORLD);

if (iproc == 0) {

printf("Estimation of pi is %f\n", sum);

}

MPI_Finalize();

return(0);

}

```

#### 2.3 Synchronous Aggregate Communication Model

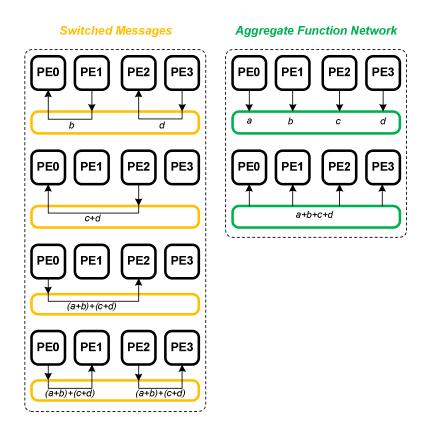

Dietz, et al. [11, 38] proposed the synchronized aggregate communication model for clusters of workstations, implemented using off-chip custom network hardware and the associated API. The communication model is neither message-passing nor shared memory, but is based on the concept of synchronously aggregating data from a group of processing elements. As shown in the right side of Figure 2.5, the off-chip aggregate function network collects an aggregate of the data items from all processing elements in the current barrier, performs a synchronous collective operation on the aggregated data, and then each processing element obtains the result of the operation from the aggregate function network. The network hardware, an aggregate function *network*, is connected to the workstations via parallel ports and provides a cluster of workstations with a fast barrier synchronization mechanism. Immediately after the barrier synchronization, processing elements may additionally perform a communication operation, called a synchronous aggregate communication or a synchronous *collective operation.* This communication model is efficient for collective operations because the communication is not point-to-point and the computation is done on the network. In the message passing version of the operation, shown in the left side of Figure 2.5, data must be communicated to processors in several steps, with accumulated totals being formed in each step.

*Collective communication* is another name for aggregate functions, most often used when referring to aggregate functions that are constructed using multiple messagepassing operations.

#### AFAPI

The Aggregate Function API (AFAPI) library [38] was initially designed for the aggregate function clusters, such as various types of PAPERS clusters. Later it was ported to shared memory multiprocessors and clusters of Linux systems. AFAPI provides parallel systems with a model that offers a good target for compilers by

Fig. 2.5. Differences between the message-passing communication model (shown on the left) and the synchronous aggregate communication model

combining low latency with predictable performance. Figure 2.6 shows an AFAPI version of the pi.

```

#include <stdlib.h>

#include <stdio.h>

#include <AFAPI/afapi.h>

int main(int argc, char **argv) {

register double width, sum;

register int intervals, i;

/* check-in with AFAPI */

if (p_init()) exit(1);

/* get the number of intervals */

intervals = atoi(argv[1]);

width = 1.0 / intervals;

/* do the local computations */

sum = 0;

for (i=IPROC; i<intervals; i+=NPROC) {</pre>

register double x = (i + 0.5) * width;

sum += 4.0 / (1.0 + x * x);

}

/* sum across the local results & scale by width */

sum = p_reduceAdd64f(sum) * width;

/* have only the console PE print the result */

if (IPROC == CPROC) {

printf("Estimation of pi is %14.12lf\n", sum);

}

/* check-out */

p_exit();

exit(0);

}

```

```

#include <stdlib.h>

#include <stdio.h>

#include <upc_relaxed.h>

upc_lock_t *lock0;

shared double pi;

int main(int argc, char **argv) {

register double width, sum;

register int intervals, i;

lock0 = upc_all_lock_alloc();

/* get the number of intervals */

intervals = atoi(argv[1]);

width = 1.0 / intervals;

upc_barrier;

/* do the local computations */

sum = 0;

upc_forall (i=0; i<intervals; i++; i) {</pre>

register double x = (i + 0.5) * width;

sum += 4.0 / (1.0 + x * x);

}

/* sum across the local results & scale by width */

pi = 0;

upc_lock(lock0);

pi += sum * width;

upc_unlock(lock0);

/* ensure all is done */

/* have only the console PE print the result */

upc_barrier();

if(MYTHREAD==0)

printf("Estimation of pi is %14.12lf\n", pi);

upc_lock_free(lock0);

exit(0);

}

```

Fig. 2.7. A UPC version of pi.c

# 3. ON-CHIP SYNCHRONOUS AGGREGATE COMMUNICATION MODEL AND ISA EXTENSIONS

In this chapter, we describe the proposed on-chip synchronous aggregate communication model and instruction set architecture (ISA) extensions for on-chip aggregate communication model.

#### 3.1 On-Chip Synchronous Aggregate Communication Model

The on-chip synchronous aggregate communication model is intended for a single socket processor with multiple cores, where a team of multiple threads are controlled by an operating system.

The major difference between aggregate communication models for off-chip and on-chip is the thread migration support. The on-chip synchronous aggregate communication model allows a team of threads to access the on-chip aggregate function network from any cores in the system.

We now provide an overview of the on-chip aggregate communication model in the context of the SPMD (Single Program Multiple Data) parallel execution model, where a team of threads executes a single program.

#### 3.1.1 Overview

A thread using an aggregate function network performs a synchronous collective operation in three phases: (1) an initiation phase, to request a synchronous collective operation and send data to that operation, (2) a waiting phase, during which a thread waits for the result of the operation to be available and then receives that operation, and (3) a completion phase, to acknowledge the receipt of the result and to inform the AFN that the thread is about to proceed past the operation.

A team of threads requests, and is assigned, a unique team number (afuID) by the AFN. Prior to any collective operation, each thread is also assigned a unique thread number (rank) within a team. For synchronous collective communication operations, each thread executes a pair of instructions: *checkin* and *checkout*. The checkin instruction is of the form AFN*OP*, where *OP* specifies a collective operation such as a barrier synchronization or a reduction. The checkout instruction is of the form AFN*OP*RD, where *OP* is as before. Use of checkin and checkout instructions for a single collective operation allows other instructions to be scheduled between the checkin and checkout instructions (i.e., the initiation and completion phases), and, as explained shortly, allows a participating thread to execute checkin and checkout instructions in different cores, enabling thread migration.

When a thread executes an AFNOP checkin instruction, the CPU core sends the opcode and any needed data to the AFN to initiate the synchronous collective operation. When a thread executes the AFNOPRD checkout instruction, the CPU core sends its *core id* (cores ids are from  $0 \dots number$  of *cores* – 1) to the AFN, and then waits for the result to be sent by the AFN. Upon the receiving the result from the AFN (as the result of a checkout instruction), the CPU core sends an acknowledgment to the AFN, and the synchronous operation is finished.

Each team of threads is assigned a secureID by the operating system that is used to ensure that a thread initiating or participating in an AFN operation on some AFU is part of the team that is associated with the AFU. secureID, afuID, and the rank constitutes a so-called SAR address, which serves as an implicit operand for the AFNOP and AFNOPRD instructions. The SAR address is sent to the on-chip AFN along with opcode and other explicit operands of AFN instructions. Both the SAR and use of split functions allow the AFN to be safely used in a multi-programmed, preemptively scheduled, system.

#### 3.1.2 Thread Migration Support

In a multicore system, a thread may be initially assigned to one CPU core and later be migrated to another CPU core by the OS. This migration may occur during the execution of a collective communication. To support thread migration, a pair of AFN instructions (checkin and checkout instructions) is used for each collective communication. First, a thread initiates a collective communication with an AFN*OP* checkin instruction, and then obtains the result of the collective communication from the AFN with an AFN*OP*RD checkout instruction. The checkin and checkout instructions do not have to be executed in the same core. The checkout instruction allows the AFN to send the result of the collective communication to the core hosting the thread that executes the checkout instruction.

The on-chip AFN does not need to track the migration of threads across cores, nor does it need to "wake-up" sleeping threads. When the operating system contextswitches out a stalled thread that is waiting for the result of an AFN operation while executing the AFN *OP*RD instruction, the AFN *OP*RD instruction will not have committed. After the thread is scheduled (perhaps on another core), it will need to re-issue the AFN *OP*RD instruction. When a thread receives the result from the AFN, the AFN *OP*RD instruction will be retired.

Whether the checkout instruction is implemented as blocking or busy-waiting, it may be possible that the result from the on-chip AFN may arrive at the core after a thread has been moved from the core by the OS. In order to provide the migrated thread with the result when it is rescheduled, the on-chip AFN is not allowed to complete the current operation and the CPU core is required to send the acknowledgment to the on-chip AFN upon the receipt of the result.

#### 3.1.3 Blocking vs. Busy-waiting AFNOPRD Instructions

Types of synchronization can be either blocking or busy-waiting. Busy-waiting is preferable when the scheduling overhead is larger than expected wait time, or proces-

```

afn_barrierSync_blocking() {

asm volatile("afnbarr_cin");

asm volatile("afnbarr_cout_block");

}

```

Fig. 3.1. AFN Checkout Instruction with Blocking

```

afn_barrierSync_busywaiting() {

asm volatile("afnbarr_cin");

while (cond)

asm volatile("afnbarr_cout_busywait");

}

```

Fig. 3.2. AFN Checkout Instruction with Busy-Waiting

sor resources are not needed for other tasks. For the on-chip aggregate communication model, the checkout instructions can be implemented using either blocking or busywaiting, as shown in Figure 3.1 and Figure 3.2, respectively. Busy-waiting might be more flexible and may allow for intelligent backoff. Unlike cache coherent shared memory, busy-waiting actually increases the network traffic between the on-chip AFN and the core. On the other hand, blocking will significantly reduce the network traffic and dynamic instruction count. For our experimental results we have assumed the busy-waiting implementation. For the performance evaluation, we use busy-waiting due to easier implementation in the simulation environment.

#### 3.1.4 Security

A team of threads is assigned a secureID by the OS using privileged instructions. The secureID is stored in the AFNSAR register. The contents of AFNSAR register can only be manipulated and read by privileged instructions. When a thread initiates an AFN operation, requests the result, or sends an acknowledgment to the on-chip AFN, secureID is sent to the on-chip AFN for authentication and must match the value at the on-chip AFN. Should the secureID not match, the AFU will throw an exception. The secureID prevents a buggy or malicious thread from another process participating in a communication operation that it should not be a part of.

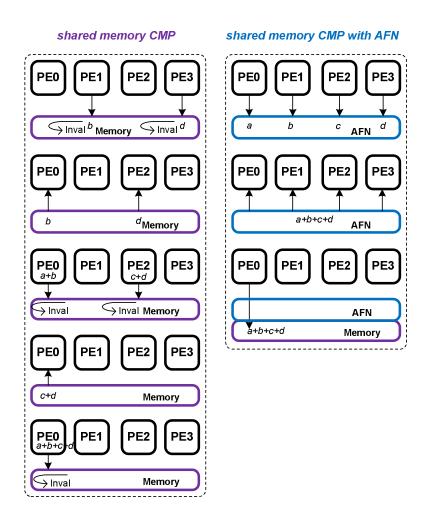

Fig. 3.3. Differences Between Cache-Coherent Shared Memory CMP without and with the on-chip AFN

#### 3.1.5 Comparison

Figure 3.3 shows differences in the execution of collective operation (reduction) between the on-chip shared memory communication model and the on-chip synchronous aggregate communication model. With the on-chip aggregate communication model, the collective operation does not generate coherence protocol messages and does not require PE's involvement for the computation.

#### 3.2 ISA Extensions for the On-Chip AFN

In this section, we describe ISA extensions for the on-chip AFN (*AFN extensions* for short) to the Intel IA32 architecture [39]. The AFN extensions do not require a specific base ISA, but should be applicable to an arbitrary ISA. AFN extensions use the synchronous aggregate communication model [11]. The extensions support inter-processor data communication, barrier synchronization, and synchronous collective operations via an on-chip aggregate function network. The details of the ISA extensions are described in the Appendix A.

#### 3.2.1 AFN Programming Environment

All AFN instructions use general-purpose registers or floating-point registers for both source and destination registers. The AFN extensions provide the following resources: eight 32-bit General Purpose Registers, eight 80-bit Floating Point Data Registers, the 32-bit AFNSAR Address Register (added for the AFN extensions) and a 32-bit AFNCSR Control/Status Register (added for the AFN extensions), which contains status and control bits used in such as AFN floating-point operations.

#### 3.2.2 AFN Instructions

As shown in Table 3.1, AFN instructions are divided into five functional groups – configuration, synchronization, reduction, data movement, and state management.

AFN Configuration Instructions include AFUALLOC, which allocates an AFU for a team of threads, and AFUFREE, which frees up the AFU. These instructions can only be executed in privileged mode and associate and disassociate thread teams from an AFU.. The first operand of AFUALLOC represents the number of threads for the team. When a new team of threads is created, an AFU is assigned using the AFUALLOC instruction. The on-chip AFN returns the afuID to the CPU core that executes the AFUALLOC instruction. When no AFU is available for the new team, the on-chip AFN

| AFN Configuration Instructions |                                    |  |  |  |

|--------------------------------|------------------------------------|--|--|--|

| AFUALLOC                       | Allocate an AFU                    |  |  |  |

| AFUFREE                        | Free up an AFU                     |  |  |  |

| Synchronization Instructions   |                                    |  |  |  |

| AFNBARR                        | Barrier Synchronization            |  |  |  |

| AFNBARRRD                      | Barrier Synchronization Read       |  |  |  |

| AFNLOCK                        | Mutex Lock                         |  |  |  |

| AFNUNLOCK                      | Mutex Unlock                       |  |  |  |

| Reduction Instructions         |                                    |  |  |  |

| AFNADD/AFNFADD/AFNFADDP        | Reduce ADD                         |  |  |  |

| AFNMUL/AFNFMUL/AFNFMULP        | Reduce MULTIPLY                    |  |  |  |

| AFNAND                         | Reduce Bitwise AND                 |  |  |  |

| AFNOR                          | Reduce Bitwise OR                  |  |  |  |

| AFN OPRD                       | Read Result                        |  |  |  |

| Data Movement Instruction      | s                                  |  |  |  |

| AFNPUT/AFNGET                  | Multi-broadcast Data Communication |  |  |  |

| State Management Instructions  |                                    |  |  |  |

| LDAFNCSR                       | Load AFNCSR Register               |  |  |  |

| STAFNCSR                       | Store AFNCSR Register State        |  |  |  |

| LDAFNSAR                       | Load AFNSAR Register               |  |  |  |

| STAFNSAR                       | Store AFNSAR Register State        |  |  |  |

Table 3.1AFN Instructions by Group

clears the most significant bit of the afuID. The user AFN operations will trap if the most significant bit of the afuID is zero, then AFN operations will be performed via software emulation, not via on-chip AFN hardware. This allows virtualization of the on-chip AFU and correct execution of programs when the number of thread teams exceeds the number of AFUs in the system.

AFUFREE takes no operands. The CPU that executes AFUFREE instruction extracts the afuID from AFNSAR and then sends the afuID to the on-chip AFN.

The synchronization instructions are AFNBARR and AFNBARRD, which perform a barrier synchronization and AFNLOCK and AFNUNLOCK, which perform a mutex lock and a mutex unlock using the on-chip AFN.

The reduction instructions are AFNOP and AFNOPRD, which perform a reduction operation. OP can be ADD, MUL, AND, and OR for reduce add, reduce multiply, bitwise AND, and bitwise OR, respectively. AFNOP copies the operand (source operand) to the on-chip AFN. For AFNADD, the on-chip AFN adds up the aggregated data from all threads.

Data movement instructions are AFNPUT and AFNGET, which perform a multibroadcast PutGet operation. AFNPUT takes two operands. The first operand is the datum for the multi-broadcast and the second operand represents the rank of the thread where the data comes from.

Finally, the state management instructions are LDAFNCSR and STAFNCSR. LDAFNCSR loads the source operand into the AFNCSR control and status register. The source operand is a 32-bit memory location. The STAFNCSR instruction stores the contents of the AFNCSR register into memory.

## 4. ON-CHIP AFN ARCHITECTURE

## 4.1 Baseline CMP-AFN Architecture

Our baseline CMP architecture uses multiple CPU cores, shared L2 cache, and the ring interconnect, similar to the Larrabee many-core architecture [40], as shown in Figure 4.1. The number of cores and L2 cache banks are implementation-dependent, as is the position of the on-chip AFN.

## 4.2 AFU-core Interconnect

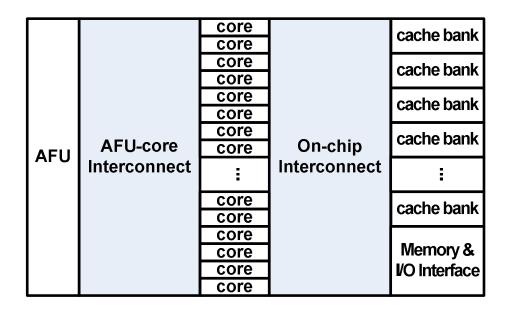

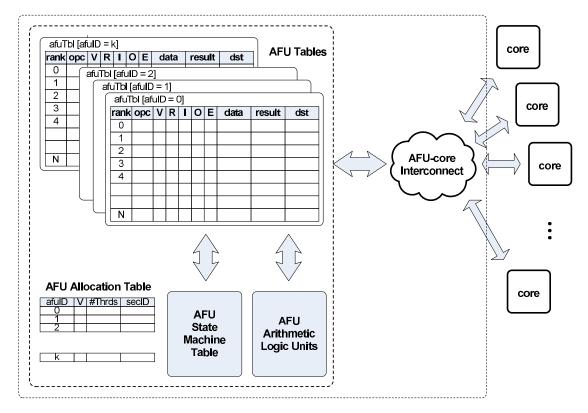

The on-chip AFN consists of the AFU-core interconnect and the aggregate function units (AFU) as shown in Figure 4.2. The AFU-core interconnect could be a dedicated interconnect or could be embedded in the existing interconnect network.

|                                    | <br>                 |                      |            |                      |                      |              |

|------------------------------------|----------------------|----------------------|------------|----------------------|----------------------|--------------|

| On-C                               | CPU core<br>L1 cache | CPU core<br>L1 cache |            | CPU core<br>L1 cache | CPU core<br>L1 cache |              |

| / diu;                             |                      | Interproce           | essor Ring | g Network            |                      | Me           |

| Un-Unip Aggregate Function Network | Coherent<br>L2 cache | Coherent<br>L2 cache |            | Coherent<br>L2 cache | Coherent<br>L2 cache | Memory & V   |

| e Functio                          | Coherent<br>L2 cache | Coherent<br>L2 cache |            | Coherent<br>L2 cache | Coherent<br>L2 cache | O Interfaces |

| Net                                |                      | Interproce           | essor Ring | g Network            |                      | Ses          |

| WORK                               | CPU core<br>L1 cache | CPU core<br>L1 cache | ••••       | CPU core<br>L1 cache | CPU core<br>L1 cache |              |

Fig. 4.1. A Baseline CMP architecture with on-chip AFN, similar to Larrabee, where the ring network is the interprocessor network that connects multiple cores and L2 cache banks. The number of cores and L2 cache banks are implementation-dependent. (Adapted from Seiler et. al 2008)

Fig. 4.2. On-Chip AFN Architecture: On-chip AFN consists of AFU and AFU-core Interconnect.

In our baseline architecture, the on-chip AFN is attached to the ring interprocessor network. The communication between the on-chip AFN and cores is done through the AFU-core interconnect. A dedicated interconnect for the AFU-core interconnect requires additional wires and logics. Alternatively, the AFU-core interconnect could be a virtual channel with the highest priority over the existing interconnect network, similar to the Cray T3E's logical barrier/eureka network [41]. The dedicated interconnect and virtual channel implementations have design trade-offs of latency versus on-chip real-estate.

The on-chip AFN and CPU cores communicate with each other via AFN request and response packets along the AFU-core interconnect. CPU cores send *AFN request packets* to the on-chip AFN. In response to the request packets, the on-chip AFN sends *AFN response packets* to the requesting CPU. As shown in Table 4.1, an AFN

| instructions | core-to-AFU packets |               |                       | AFU-to-core packets    |        |

|--------------|---------------------|---------------|-----------------------|------------------------|--------|

| Instructions | opcode              | operand       | SAR                   | status                 | result |

| AFUALLOC     | opcALLOC            | numThrds      | secureID              | error, complete        | afuID  |

| AFUFREE      | opcFREE             | -             | secureID, afuID       | error, complete        | -      |

| AFNBARR      | opcBARR             | -             | secureID, afuID, rank | error, complete        | -      |

| AFNBARRRD    | opcBARRRD           | -             | secureID, afuID, rank | error, complete, retry | -      |

| AFNLOCK      | opcLOCK             | -             | secureID, afuID, rank | error, complete, retry | -      |

| AFNUNLOCK    | opcUNLOCK           | -             | secureID, afuID, rank | error, complete, retry | -      |

| AFNADD       | opcADD              | data          | secureID, afuID, rank | error, complete        | -      |

| AFNMUL       | opcMUL              | data          | secureID, afuID, rank | error, complete        | -      |

| AFNAND       | opcAND              | data          | secureID, afuID, rank | error, complete        | -      |

| AFNRD        | opcRD               | -             | secureID, afuID, rank | error, complete, retry | data   |

| AFNFADD      | opcFADD             | data          | secureID, afuID, rank | error, complete        | -      |

| AFNFMUL      | opcFMUL             | data          | secureID, afuID, rank | error, complete        | -      |

| AFNFRD       | opcFRD              | -             | secureID, afuID, rank | error, complete, retry | data   |

| AFNPUT       | opcPUT              | data, srcThrd | secureID, afuID, rank | error, complete,       | -      |

| AFNGET       | opcGET              | -             | secureID, afuID, rank | error, complete, retry | data   |

| -            | opcRDACK            | _             | secureID, afuID, rank | -                      | _      |

Table 4.1

Packets to communicate between CPU cores and on-chip AFN

request packet contains the SAR address, opcode, and data. An AFN response packet contains the SAR address, status, and result. The on-chip AFN extracts appropriate information from incoming request packets, processes the packets, and creates the response packets based on the table shown in Table 4.1.

As the on-chip AFN may broadcast the result of collective communications to all cores, it may leverage the hardware support for multicast such as VCTM (Virtual Circuit Tree Multicasting) [42]. VCTM supports multicast of network messages, such as invalidation messages from the coherence protocol, in the network on chip (NoC).

## 4.3 Aggregate Function Unit

In this section, we describe AFU, which consists of AFU tables, state machines, aggregate ALUs and an AFU allocation table, as shown in Figure 4.2.

## 4.3.1 AFU Tables

Each AFU table keeps various information for a team of threads and is indexed by afuID, i.e. afuTbl[afuID]. Per-thread information in each table is indexed by thread's rank, i.e. afuTbl[afuID][rank], and stores opcode (opc), 5-bit state (V/R/I/O/E), data, and core number. V stands for valid, R for RESET, I for INPUT\_ARRIVED, O for OUTPUT\_READY, E for ERROR. afuTbl[afuID]. INPUT\_ARRIVED[N:0] is an arrived vector, where each bit position indicates whether the corresponding thread has arrived or not.

## 4.3.2 AFU State Machines

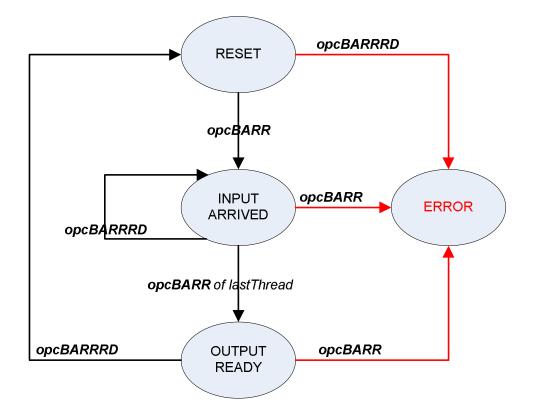

AFUs use state machines to process AFN operations. An AFU maintains a state machine for each AFN operation. And for each AFN operation, one state machine exists per thread, and are updated when qualified events occur, including the arrival of an AFN opcode from the core. Figure 4.3 shows the state machine for AFNBARR/AFNBARRRD (barrier synchronization). The state machine consists of four states, RESET, INPUT\_ARRIVED, OUTPUT\_READY, and ERROR. RESET is the initial state and indicates that the corresponding thread is waiting for the request packet with opcode opcBARR to arrive at the AFU. Upon the arrival of opcBARR packet for the thread, the AFU changes the state from RESET to INPUT\_ARRIVED. The INPUT\_ARRIVED state indicates that the thread is waiting for opcBARR packets of other threads in a team to arrive at the AFU. When all threads arrives at the AFU (i.e., VALID[N:0] == INPUT\_ARRIVED[N:0]), the states for all threads become OUTPUT\_READY. The OUTPUT\_READY state indicates that the thread is waiting for the packet with opcode opcBARRRD to complete the barrier synchronization. Upon the arrival of opcBARRRD packet, the AFU changes the state to RESET for the corresponding thread. **RESET** state indicates that the thread is ready to take next barrier synchronization or any AFN operations.

Fig. 4.3. State Machine for Barrier Synchronization (AFNBARR/AFNBARRD)

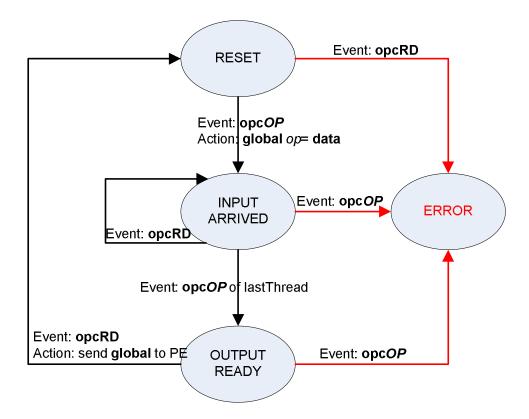

We note that threads in a team may not all change their states back to RESET at the same time. However, the AFU does not prevent threads in the RESET state from entering the next barrier synchronization even if there are threads whose states are OUTPUT\_READY for the previous barrier synchronization. The state machine for AFN*OP*/AFN*OP*RD is shown in Figure 4.4, which is similar to that of barrier synchronization.

## 4.3.3 Aggregate Function ALUs

A collective operation is an N-operand operation and can be implemented using a binary ALU with multiple iterations or using N-ary ALU with a single iteration. There is a design trade-offs. In principle, the AFU waits for all operands to arrive

Fig. 4.4. State Machine for Reduction Operation (AFNOP/AFNOPRD)

(i.e. all threads reach synchronization point) to perform N-operand computation of the aggregate function that is specified by the opcode.

But, in practice, the computation of the N-operand aggregate function may begin as operands arrive at the AFU (before all operands arrive) and the AFU may perform the computation as a binary operation of a newly arrived operand and the accumulated result. With this reason, an expensive N-ary ALU may not be required.

## 4.3.4 AFU Allocation Table

The AFU allocation table keeps track of outstanding teams of threads that use the on-chip AFN for the collective operations. When a team of threads is assigned an afuID, the corresponding entry (indexed by the afuID) is allocated for the team of threads and stores appropriate information.

## 4.4 A Case for CMP-AFN

In this section, the analytical model for the barrier synchronization will be discussed.

## 4.4.1 Barrier Synchronization Latency for CMP-AFN

From each thread's perspective, the latency  $(T_{AFN\_instr})$  of AFN instructions can be defined as follows:

$$T_{AFN\_instr} = T_{Core\_to\_AFN} + T_{load\_imbalance} + T_{BPL} + T_{AFPL} + T_{AFN\_to\_Core\_to\_AFN} + T_{AFN\_to\_COFAFN} + T_{AFN\_to\_COFAFN} + T_{AFN\_to\_Core\_to\_AFN} + T_{AFN\_to\_$$

For barrier synchronization,  $T_{AFPL} = 0$ . Therefore, when all threads start to execute the barrier instruction at the same time (i.e.  $T_{load\_imbalance} = 0$ ), the latency for barrier synchronization will be as follows:

$$T_{barr\_cmpafn} = T_{Core\_to\_AFN} + T_{BPL} + T_{AFN\_to\_Core}$$

# Table 4.2A Case for CMP-AFN

| Latencies and Configuration                           |

|-------------------------------------------------------|

| CMP 4 cores                                           |

| L1 $64k+64k$ , $64B$ line                             |

| L1 latency 3 cycles                                   |

| Shared L2 4 banks: 1 local and 3 remote               |

| Shared L2 local/remote latency: 15/20 cycles          |

| Write-back to read latency: 35-40 cycles              |

| Transit time between core and AFN (one-way): 7 cycles |

| Barrier sync latency within AFN: 3 cycles             |

| Reduction latency within AFN: 10 cycles               |

| PutGet latency within AFN: 6 cycles                   |

| $T_{mutex\_lock}$       | 20 | read mutex_var from L2              |  |  |

|-------------------------|----|-------------------------------------|--|--|

| $T_{mutex\_unlock}$     | 20 | write-back mutex_var to L2 $$       |  |  |

| $T_{++arr}$             | 21 | read arrived from L2 and increment  |  |  |

| $T_{arr}$               | 21 | read arrived from L2 and decrement  |  |  |

| $T_{sem\_post}$         | 21 | read sem_post from L2 and decrement |  |  |

| $T_{core2afn\_transit}$ | 7  | transit time from core to AFN       |  |  |

| $T_{afn2core\_transit}$ | 7  | transit time from AFN to core       |  |  |

Table 4.3 GOMP latencies

#### 4.4.2 Barrier Synchronization Latency in a conventional CMP

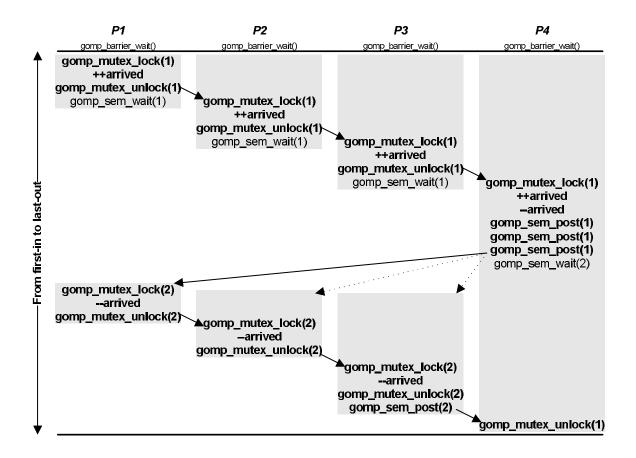

gomp\_barrier\_wait() is the GNU implementation of barrier synchronization. As illustrated in Figure 4.5, it uses a shared variable arrived. Its execution consists of three stages- arrival stage, wake-up stage, and re-initialization stage. In the arrival stage, when a thread arrives at a barrier, it increments the arrived shared variable, then spin-wait using gomp\_sem\_wait(). When the last thread arrives at the barrier, it wakes-up the prior N-1 threads by calling gomp\_sem\_post() N-1 times (the wake-up stage). Then, all other threads atomically decrement arrived to re-initialize to zero for next barrier use (the re-initialization stage).

Bold faced functions in Figure 4.5 represent codes in the critical path of the latency. Therefore, the latency of gomp\_barrier\_wait() for N threads can be represented as follows:

$$T_{gomp\_barr} = \sum_{p=1}^{N} (T_{mutex\_lock} + T_{++arr} + T_{mutex\_unlock}) + \sum_{p=1}^{N} T_{sem\_post}$$

$$+ \sum_{p=1}^{N} (T_{mutex\_lock} + T_{--arr} + T_{mutex\_unlock})$$

Table 4.3 lists *minimum* time to take each function that are listed in the above latency equation. For example, the time for gomp\_mutex\_lock() will vary at run-

|                       | latencies   |

|-----------------------|-------------|

| $T_{barr\_cmp\_afn}$  | 17 cycles   |

| $T_{gomp\_barr}$      | 572  cycles |

| $T_{gomp\_barr\_log}$ | 286 cycles  |

Table 4.4barr sync latency comparison

time due to lock contention and the Table shows the minimum time to execute the function.

gomp\_barrier\_wait() does not parallelize the arrival stage, as illustrated in Figure 4.5. In other words, even if all threads arrive at a barrier at the same time, arrived is incremented sequentially. If more than one shared variables are used, the arrival stage can be executed in parallel. In this case, the latency is as follows:

$$T_{gomp\_barr\_log} = \sum_{p=1}^{\log N} (T_{mutex\_lock} + T_{++arr} + T_{mutex\_unlock}) + \sum_{p=1}^{\log N} T_{sem\_post} + \sum_{p=1}^{\log N} (T_{mutex\_lock} + T_{--arr} + T_{mutex\_unlock})$$

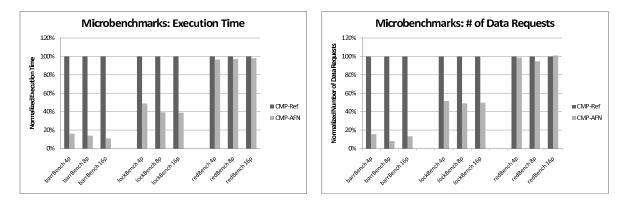

Fig. 4.5. gomp\_barrier\_wait() when all four threads arrived a barrier at the same time

## 5. EVALUATION METHODOLOGY AND RESULTS

The evaluation has been done using a cycle-accurate full-system simulation of a single chip shared-memory multi-core processor using *Simics* [43] and *GEMS* [44]. We evaluate CMP-AFN against CMP without on-chip AFN (CMP-REF), with various core counts. We use the EPCC OpenMP Microbenchmarks [7] and the SPEC OMP (OpenMP Benchmark Suite) [45–47] for the evaluation. We compiled and ran OpenMP benchmarks using GOMP (GNU OpenMP), an OpenMP implementation for GCC [5,48].

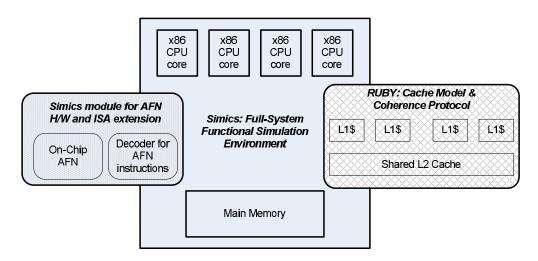

## 5.1 Simulation Target Configurations

Simics is a full-system functional simulator that models various instruction set architectures and can execute commercial applications and operating systems. We created six Simics simulation targets – three CMP-REF (4, 8, and 16 cores) and three CMP-AFN targets (4, 8, and 16 cores). A 4-core CMP-AFN target is shown in Figure 5.1. All CMP-REF and CMP-AFN targets have Fedora Core 5 installed and contain IA32-based cores, 512 MB memory, and one 19GB IDE disk. Fedora Core 5 features Linux kernel 2.6.15 with SMP support and Native POSIX Thread Library (NPTL) version 2.4, which supports Futex (Fast Userspace Mutex) [4].

GEMS's Ruby enables the models of the cache memory hierarchy, the protocol controllers, and the on-chip interconnect in all simulation targets. It provides performance statistics for all cache and memory activities. Each target has a 32K-Byte private L1 cache for each core and 1 MByte-per-core shared L2 cache. These values are not intended to model a specific commercial chip, but to approximate the cache structure one might reasonably expect for a many-core design. The latest (64-bit extended) IA32-based 4-core Intel Core i7 and AMD Phenom II chips use 32K to

Fig. 5.1. A four-core CMP-AFN Simics Target

64K L1 caches. Our L2 cache design approximates the 6M to 8M shared L3 caches of those chips. We used Ruby's  $\widehat{\text{MOESI\_CMP\_directory}}$  for the on-chip cache coherence protocol. It is an on-chip two-level directory protocol using non-inclusive L1/L2 caching with blocking caches. This directory-based cache coherence protocol was selected because it scales better with higher core counts than a snoopy protocols.

For CMP-AFN targets, we developed a Simics module to implement on-chip AFN hardware logic and the instruction decoder for the AFN ISA extensions. We load the AFN instruction decoder module into the CMP-REF targets, as shown in Figure 5.1, to create CMP-AFN targets. The transit time between a core and an L2 cache bank is the one-way latency of a memory request traveling from the core to one of the L2 cache controllers through the on-chip interconnect. The same amount of time is used for the transit time between a core and the on-chip AFN. Table 5.1 shows system configurations for the target architectures. We used Simics version 3.0.29 and GEMS version 1.4. To use Ruby with the IA-32 architecture-based Simics targets, we created a Ruby patch for the IA-32 architecture for GEMS version 1.4, which has been integrated and released as part of GEMS version 2.0.

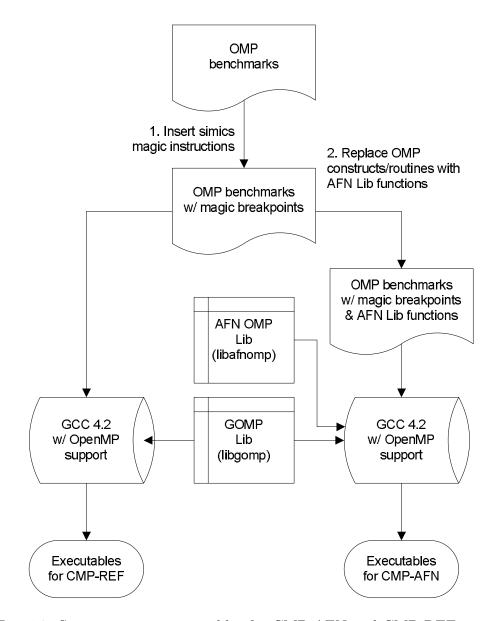

## 5.2 Re-targeting OpenMP Benchmarks for CMP-AFN

For the CMP-AFN architecture, synchronization primitives and thread management methods can be ported using AFN instructions to utilize the on-chip AFN for collective operations in the OpenMP applications. Because an OpenMP runtime library for the CMP-AFN does not exist, we replaced OpenMP constructs/routines in the OpenMP benchmark with the corresponding *AFN Library routines for OpenMP*. The AFN Library routines for OpenMP include AFN instructions and perform OpenMP barrier synchronization, lock, and reductions through the on-chip AFN in the target. Table 5.2 shows conversions from OpenMP constructs/routines to AFN library routines for OpenMP. Although we manually performed the conversion, this can also be done with an automatic source-to-source translator. We compiled the

| [                |                                           |  |  |

|------------------|-------------------------------------------|--|--|

| CPU Cores        | Intel Pentium 4, in-order                 |  |  |

|                  | 4-core, 8-core, and 16-core               |  |  |

| Private L1 Cache | 32KB 4-way, 64Byte-line                   |  |  |

| Frivate L1 Cache | L1 hit latency: 1-cycle                   |  |  |

|                  | 4-core CMPs: 4MB, 4 banks, 16-way         |  |  |

| Shared L2 Cache  | 8-core CMPs: 8MB, 8 banks, 32-way         |  |  |

|                  | 16-core CMPs: 16MB, 16 banks, 64-way      |  |  |

| Cache Coherence  | Directory Based Protocol                  |  |  |

| Protocol         | i.e. $Ruby$ 's MOESI_CMP_directory        |  |  |

| Main Manager     | 512MB total memory                        |  |  |

| Main Memory      | 200-cycle memory access                   |  |  |

|                  | Tango (Fedora Core 5)                     |  |  |

| Platform         | Linux kernel 2.6.16                       |  |  |

| Platform         | NPTL 2.4 (Native Pthreads Lib) with Futex |  |  |

|                  | GCC 4.2.1 with OpenMP support             |  |  |

Table 5.1Configurations for Simulated Targets

| OpenMP Constructs/Routines             |            | AFN Lib Routines for OpenMP |

|----------------------------------------|------------|-----------------------------|

| #pragma omp barrier                    | $\implies$ | afn_barrier_omp();          |

| <pre>#pragma omp critical</pre>        |            | afn_lock_omp();             |