# iAPX286 Compiler Writer's Guide

Ву

Al Hartmann

Intel Corporation

Version #1

May 1983

# © Copyright Intel Corporation, 1983

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products:

BXP. CREDIT, i, ICE, ICS, i<sub>m</sub>, iMMX, Insite, Intel, int<sub>e</sub>t, Intelevision, Intellec, iOSP, IRMX, ISBC, ISBX, Library Manager, MCS, Megachassis, Micromainframe, Micromap, Multimodule, Plug-A-Bubble, PROMPT, RMX/80, System 2000 and UPI.

# iAPX 286 Compiler Writer's Guide

| Tab | le of Contents                                        |

|-----|-------------------------------------------------------|

| 1.  | iAPX 286 Architecture Sketch                          |

| 2.  | Program Addressing                                    |

| 3.  | Data Addressing                                       |

| 4.  | Compilation Techniques for Local Code Quality 4-1     |

| 5.  | Exceptions, Errors, Debugging, and Interpretation 5-1 |

| 6.  | The iAPX 286 Object Language 6-1                      |

| 7.  | Object Utilities                                      |

|     | References                                            |

#### INTRODUCTION

Intel's new iAPX-286 microprocessor is an extended version of the 8086 microprocessor (1,2) with a larger address space, virtual memory capability, multi-level protection mechanism, firmware support for multitasking, some additional instructions, and higher performance (2-3X). Other articles describe the 286 itself (3,4), operating system design for the 286 (5), and the software design rationale for the 86 family architecture (6). This article describes programming language implementation for the 286, covering 286-specific compiler targeting issues, post-compilation object processing, and debugging. Section 1 sketches the 286 processor architecture from a language impelentator's viewpoint, Section 2 covers program addressing, Section 3 covers data addressing, code generation is reviewed in Section 4, debugging and exception handling in Section 5, object module design in Section 6, and object utilities in Section 7.

## \*\* 1. iAPX 286 ARCHITECTURE SKETCH \*\*

The programming language implementor views the 286 architecture through different eyes than those of an operating systems designer or of an applications programmer. The ring model protection structure and tasking support are not the driving factors here (as they might be to an operating systems implementor). Basic programming language issues are the addressing model (for programs and for data), the register set, operand forms, data types, and operator types.

#### \*\* ADDRESSING IN THE LARGE \*\*

The 286 uses a segmented, byte-addressable, virtual addressing model. The virtual address space is composed of an arbitrary number of segments each of which is of any size between one and 64 Kbytes. A segment is described by a 64-bit segment descriptor (Fig. 1.1) that tells its base address, offset limit, access rights, and also contains one word reserved for future usage (5).

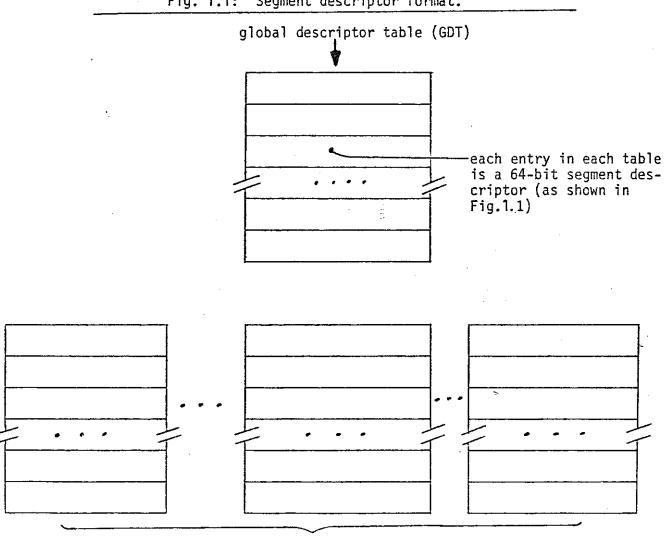

Between one and 8K segment descriptors are grouped into a segment descriptor table, which is itself a segment. There may be any number of descriptor tables, since they are stored in memory as any other segment. The system virtual address space, then, may be of unlimited size, although it will be effectively limited by the number of separate processes, or tasks, in the system. The 286 processor provides each task with immediate access to one of two descriptor tables (Fig 1.2), a global descriptor table (GDT) shared by all tasks, and a local descriptor table (LDT) that is local to that particular task. Descriptor tables are protected segments modified only by the operating system. The operating system establishes the global table during system initialization, and the segment descriptor for the local table is part of the task state loaded by the processor during a context switch from one task to another. So the task virtual address space is defined by the system's GDT and by the task's own LDT, for a maximum of 8K local segments and 8K global segments (or conceivably a one-gigabyte address space).

| limit (16 bits)             |  |  |

|-----------------------------|--|--|

| base (24 bits)              |  |  |

| access (8 bits)             |  |  |

| software reserved (16 bits) |  |  |

Fig. 1.1: Segment descriptor format.

local descriptor tables (LDT's)

Fig. 1.2: Descriptor tables.

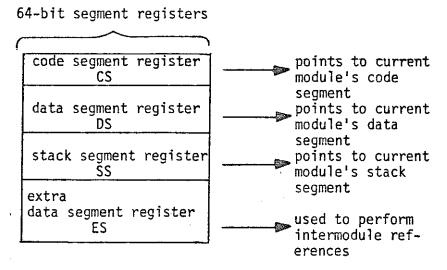

Since references over this enormous task address space are generally localized, the 286 processor contains four <u>segment registers</u> (Fig. 1.3) to hold four descriptors immediately on chip. The task itself is normally composed of program modules, each with a need to reference its code (via the code segment register, CS), its permanent data (via the date segment register, DS), its temporary data (via the stack segment register, SS), and to occasionally share other modules' data (via the extra data segment register, ES). The processor automatically loads the segment registers during context changes, or they may be explicitly loaded by program instructions. All references use one of the segment registers. Generally the appropriate segment register is implicitly known and selected by default (e.g. a branch instruction would use CS, an ordinary data reference would use DS, and a stack-relative data reference would use SS). If the default segment register choice is not the desired choice (e.g. for an inter-module reference using ES), then a one-byte segment register override prefix is added to the instruction.

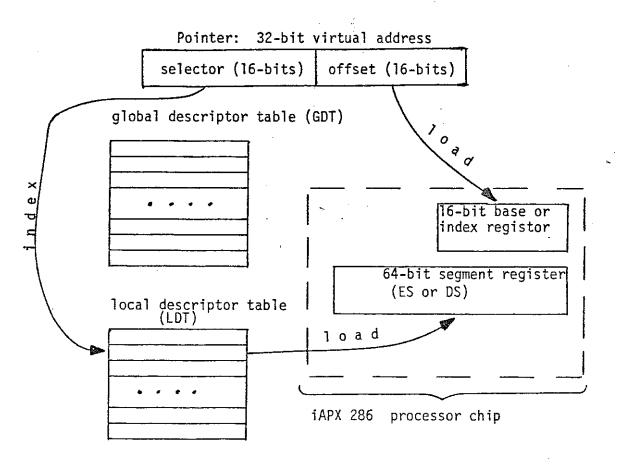

Pointers or other indirect references are 32-bit virtual addresses in the form of a 16-bit segment selector and a 16-bit segment offset. The selector selects a segment descriptor from either the global or local descriptor tables for loading into a segment register. Since the iAPX 286 does not use indirect addressing, pointers must first be loaded into processor registers prior to usage (Fig. 1.4). The instructions load-data-segment-register (LDS) or load-extra-data-segment-register (LES) load a pointer into the processor registers. The pointer's selector half selects a descriptor to be loaded into one of the segment registers, and the pointer's offset half is loaded directly into a 16-bit base or index register. One bit in the selector chooses either the local or the global descriptor table, two other bits specify the ring privilege level (2), and the remaining 13 bits index among 8K possible descriptors in the table. Note that compilers generate code dealing just with selectors; only the operating system deals directly with descriptors.

Virtual-to-physical address translation (as performed in the processor chip itself) consists of adding the effective 16-bit offset generated by the instruction's addressing mode to the 24-bit base address contained in the segment register to produce a 24-bit physical address (16 Mbytes). Limit, privilege, and access rights checking are also performed (2).

#### \*\* ADDRESSING MODES \*\*

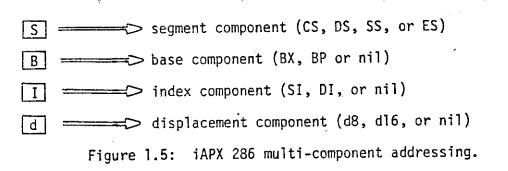

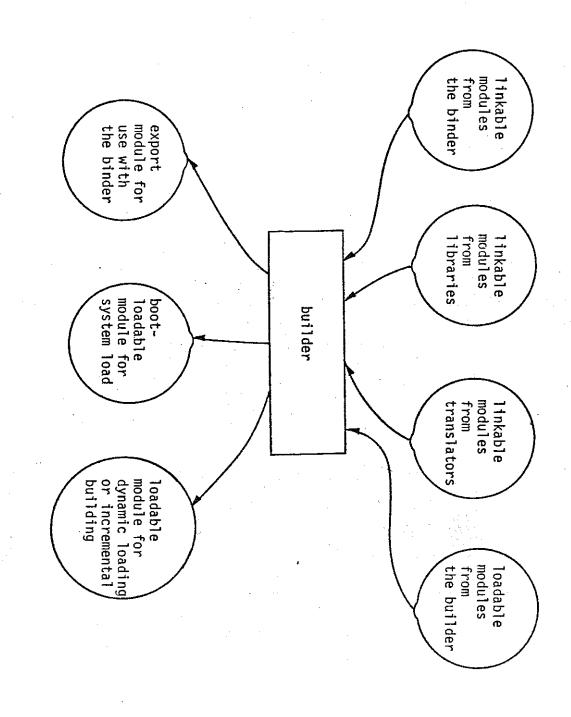

The iAPX 286 shares the addressing modes of the 8086, which are extensively described elsewhere (1). Basically a multi-component address (Fig. 1.5) is used, consisting of a segment component and of base, index, or displacement components. The segment component, as already mentioned, selects one of four available segments. Figure 1.6 shows the decomposition of a software module into three segments for storage of program code, permanent data, and temporary data. The fourth segment access available is used for inter-module references or for temporary usage. A compiler processing a single module typically emits object code for the code segment, including compiled program code and constants. Initial values of global variables may be emitted for the data segment. No initial contents are generated for the stack segment. Emitted portions of all three segments from separate compilations are combined by the binder program (Sec. 7), according to object language rules (Sec. 6).

Fig. 1.3: The four segment registers.

Figure 1.4: Pointer loading prior to usage.

code segment (module code and constants) data

segment

(permanent,

or global,

module data)

stack segment (temporary, or local, procedure data)

Figure 1.6: Division of a software module into segments.

Data references will operate in any of the segments using almost any combination of a base component, index component, and displacement component. Two sixteen-bit base registers (BX and BP) are provided, with BP usually treated as the local data base-register, since it implicitly selects the stack segment. Two sixteen-bit index registers (SI and DI) exist, and the displacement, if present, may be either eight or sixteen bits. Table 1.1 shows the address components typically selected for referencing static or dynamic scalar, vector, and record data items.

### Address Components

| Data Type | Static Form | Dynamic Form |

|-----------|-------------|--------------|

| scalar    | · d         | В            |

| vector    | d,I         | В,І          |

| record    | d           | B,d          |

Table 1.1: Typical address component usage.

#### \*\* PROGRAM TRANSFER OVERVIEW \*\*

A transfer of control may be initiated by a jump, a call, a return, or by the occurrence of an exceptional condition (trap or interrupt). Jumps may be conditional or unconditional. Conditional jumps use an 8-bit self-relative displacement. Unconditional jumps use either an 8 or 16-bit self relative displacement, or a full 32-bit virtual address. Calls use either a 16 bit self-relative displacement or a full 32-bit virtual address. For both jumps and calls, the 16-bit or 32-bit target address may be contained in the transfer instruction itself (direct transfer) or be contained in data memory (indirect transfer) and be referenced via any addressing mode. Three return forms support 16-bit intrasegment returns, 32-bit inter-segment returns, or interrupt returns. Exceptional conditions may be invoked by external or internal events, or by soft interrupt, or trap, instructions.

Transfers of control are intra-procedural (as in local jumps), inter-procedural (as in ordinary calls), or inter-task (as in calling or jumping to a task entry point). The descriptor table entry for inter-segment transfers (selected by the 16-bit selector portion of the 32-bit virtual address) indicates whether the target is a task entry or not. An inter-segment transfer may cross protection level boundaries, and this is also indicated in the descriptor table entry selected by the virtual address. A special type of entry (called a gate) is used for protection level crossings. The topics of tasking and protection support in the iAPX 286 are treated more fully elsewhere (5).

#### \*\* REGISTER SET AND OPERAND FORMS \*\*

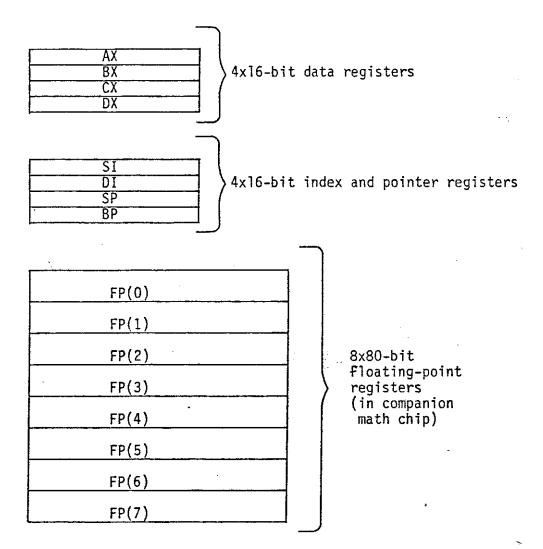

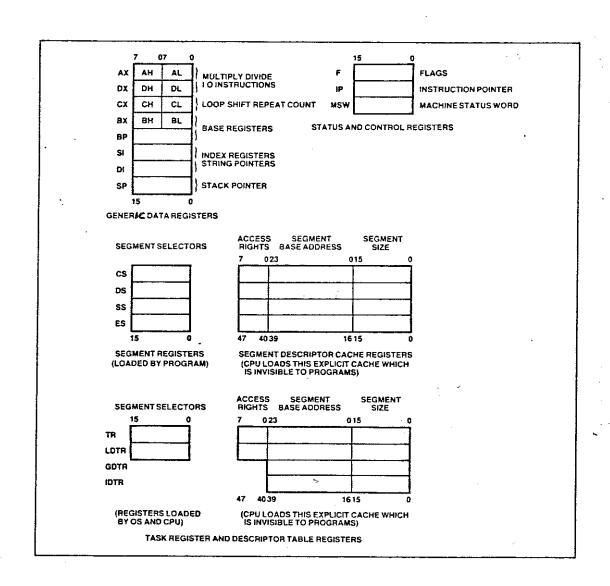

The iAPX 286 possesses working registers, segment registers, and system and status registers. The working registers are shown in Figure 1.7, and consist of eight 16-bit registers. A companion math processing chip contains eight 80-bit floating-point registers, shown in the figure.

Instructions may take zero, one, or two operands. The two operand forms in general take one register or constant operand, and one register or memory operand, except for the string instructions, which take two memory operands. The addressing modes for referencing memory operands have already been discussed. The iAPX 286 can directly mainpulate 8 or 16-bit signed or unsigned integers, while the companion math processor can operate on 16-bit, 32-bit, and 64-bit integers, and 32-bit, 64-bit, and 80-bit floating-point numbers.

Fig. 1.7: iAPX 286 working register set and floating point register set.

#### \*\* 2. PROGRAM ADDRESSING \*\*

As described in the overview, program addressing in the iAPX 286 follows the conventional pattern of conditional and unconditional branches for statements, and of call instructions for procedures and module entries. These instructions are extended by the architecture to also permit task invocation via branches or calls, rather than requiring special activation of tasks via traps or supervisor calls. Thus the processor architecture recognizes and supports inter-statement, inter-procedure, inter-module, and inter-task program transfers.

Examples of instructions generated for typical control flow statements are shown in Figures 2.1a (if-statement), 2.1b (case statement), and 2.2 (iterative loop). Note that conditional jumps use signed 8-bit displacements, and occasionally the 128-byte jump range may not be adequate. In this case the usual "jump around a jump" is employed wherein the sense of the jump condition is reversed and it jumps around a 16 or 32-bit displacement unconditional jump to the distant jump target. A simple code-generation technique for choosing between use of a normal short jump or use of a jump-around, in the case of forward branches where the displacement to the target is unknown, will be described later (Sec. 4).

Figure 2.1b shows the usual implementation of the case statement as an indexed branch. The case selector, i, is loaded into an index register, SI, scaled by 2, and used to index an indirect branch via the case table of addresses. Note that a single instruction, BOUND, performs bounds checking on the selector.

Figure 2.2 shows a typical iterative loop construction (this one from Ada) with a mid-loop conditional exit. Its implementation is straight forward and self-explanatory.

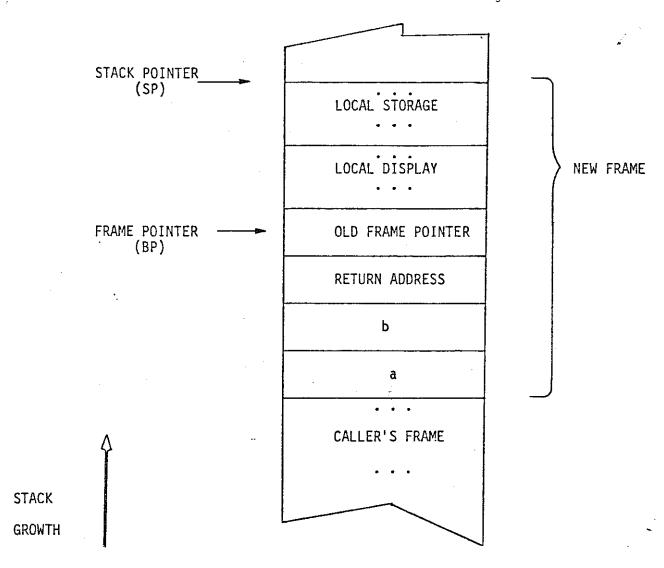

Figure 2.3a shows a procedure invocation with the usual argument push and call implementation. Figure 23b shows the procedure prologue/epilogue code, consisting of a single high-level ENTER instruction for the prologue, and a LEAVE, RETURN instruction pair for the epilogue. The PUSH instructions place the arguments on the stack, the CALL instruction deposits the return address on the stack, the ENTER instruction stores the old frame pointer (dynamic link) on the stack, copies the relevant portion of the caller's display (consisting of the base addresses of enclosing blocks' data frames and used for up-level addressing) into the local display area, adds the new frame pointer to the display, and allocates local storage for the new stack frame. The layout of the resultant stack appears in Fig. 2.4.

Where collections of data and procedures are combined into modules, as in Ada, storage for the module is allocated in one of the various program segments. This may affect the procedure prologue/epilogue for module entry procedures. Figure 2.5 shows several possibilities. In Fig. 2.5a the module is global to the entire program, so that its data is permanently allocated to the data segment for the module. So in the module entry procedure prologue the caller's DS value should be saved on the stack and the module's own DS value loaded. Then in the epilogue the caller's DS value should be restored from the stack prior to return.

Figure 2.5b shows the case of a local module whose declaration is nested within a procedure. For a small local module its data can be stored in the containing procedure's stack frame and the entry prologue/epilogue is unchanged. For a large local module, a new data segment needs to be dynamically allocated and its base address needs to be stored in a fixed location in the containing procedure's stack frame. This address then needs to be loaded into the ES register for reference to the data area prior to each such data area reference. Alternatively, the entry procedure prologue could insert the module data base address into the proper location in the local display.

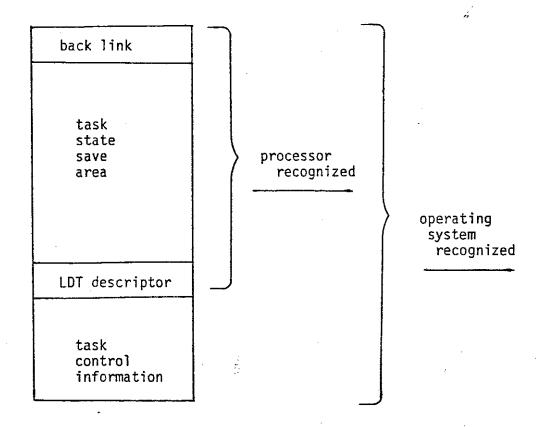

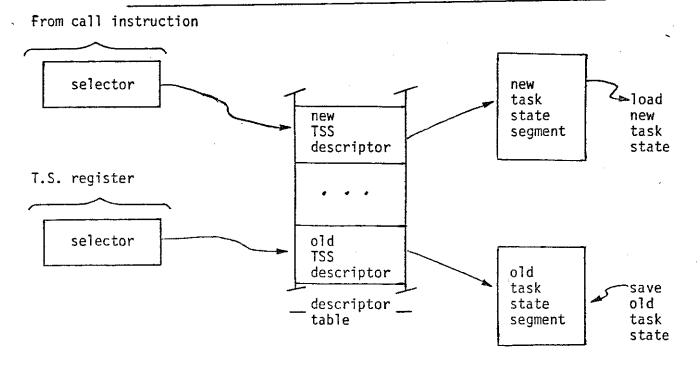

One advantage of the iAPX 286 architecture is its support for tasking. The processor recognizes task descriptors (referenced in the descriptor table through branch or call instructions) and loads new task states for execution via task state segments (TSS's) shown in Fig. 2.6. A task invocation (Fig. 2.7) saves the old task state in its TSS and loads the new task state from the new TSS as a single instruction action, making rapid, realtime context switching possible.

```

if B then S<sub>1</sub> else S<sub>2</sub>

-- evaluate B

-- jump false to start of S<sub>2</sub> code

-- code for S<sub>1</sub>

JMP next

-- jump to next statment

-- code for Sz

-- code for next statement

b)

Case i of

MOV

SI, i -- load i into index req

BOUND

SI, case tbl -- check 1 ≤ i ≤ 3

1: S;

SHL

SI, 1 -- scale i by 2

2, 3:

JMP

case tbl+2[SI] -- indexed jump thru

end

case tbl

1 -- lower index bound

case-tbl: DW

3 -- upper index bound

DW

@S_1 -- address of S_1

@S_2 -- address of S_2

@S_2 -- address of S_2

DW

code

DW

code

DM

code

code for S<sub>1</sub>

JMP next -- jump to next statement

code for S<sub>2</sub>

code for next statement

```

FIG. 2.1: a) code generated for if-statement branching

b) code generated for case-statement branching

```

For i in index'range loop

exit when B ;

end loop;

MOV

SI, index'first -- initialize SI to first value in range

loop:

CMP

SI, index'last -- check for terminators

JG

next --

jump to next statement if terminated

-- code for S<sub>1</sub>

-- code to evaluate B;

next --

jump to next statement if true

-- code for S<sub>2</sub>

INC

increment loop parameter, SI

JMP

100p

and loop

next:

next statement

FIG. 2.2: Code generated for iterative loop statement with exit condition

a)

P(a,b);

-- assume a,b scalar parameters

PUSH a

PUSH b

CALL P

b)

procedure P(x,y); . . . end;

-- procedure prologue code:

ENTER local_size, lex level -- mark stack, create display

for this lexical level,

and allocate local storage frame

-- procedure body code here

-- procedure epilogue code:

LEAVE

-- cut back stack to delete

local frame and display

RET arg-size

-- return to caller and remove

arguments from stack

a) Procedure invocation code example

FIG. 2.3:

b) Procedure prologue/epilogue code example

```

FIG. 2.4: Stack growth after procedure invocation and entry

a) global module:

——►module data stored in data segment

b) local module:

- for a small local module data area, include in stack frame storage for containing procedure;

- for a large local module data area, create an extra segment and store pointer to it in containing procedure's stack frame.

FIG 2.5: Module data storage using Ada examples

.

FIG 2.6: Task state segment (extended).

FIG 2.7: Task invocation actions

#### \*\* 3. DATA ADDRESSING \*\*

As mentioned in the overview, the 286 addressing mechanism supports references to static or dynamic scalar, vector, and record data items. These utilize the addressing mode fields (1) contained in memory reference instructions to select among the various address components already shown in Figure 1.5. To give a reasonably complete set of examples of reference forms, let's study the code generated by a Pascal procedure call with a list of integer arguments passed by value as follows:

The two constant arguments would be passed as:

PUSH byte\_constant -- two-byte instruction

PUSH word\_constant -- three-byte instruction

The byte constant is contained as a single byte in the instruction, which sign-extends the constant to 16-bits before pushing it onto the stack. The vast majority of program constants fit in a byte, making automatic sign-extension worthwhile. The larger word constant is stored in two bytes, making for a three byte instruction. Instructions in the 286 are an arbitrary number of bytes in length, allowing for more compact instruction encoding than would be possible with word-aligned instruction set restrictions.

The two scalar arguments, the static(global) argument and the dynamic (local, stack-based) argument, are passed as:

PUSH static\_scalar -- DS base + 16-bit offset

PUSH dynamic\_scalar[BP] -- SS base + BP frame ptr + 8 or

16-bit offset

The static scalar resides in the data segment and is reached with a 16-bit displacement, making for an instruction of four bytes. The dynamic scalar is assumed to reside in the current local data frame within the stack segment and is typically well within the range of an 8-bit displacement, making for a three-byte instruction. Since most data references in block structured languages such as Pascal, C, or Ada are generally to local variables and parameters, the bulk of these reference instructions are 3-byte instructions, again favoring the byte-aligned instruction set design.

If the dynamic scalar were stored in <u>another</u> data frame, belonging to an enclosing procedure, then the local display (created automatically by the ENTER instruction of the procedure prologue - Fig. 2.4) is used to indirectly reference the scalar, as follows:

MOV BX, display\_el -- load other frame base into BX PUSH SS:dynamic\_scalar[BX] -- SS base + BX frame + offset

Note that the appropriate frame base from the local display is loaded into the alternate base register, BX, in a single three-byte move instruction. This is more efficient than chasing down the so-called static chain (7) to find the enclosing frame base, as is done in many implementations. It also frees the registers from always containing the display, which is only infrequently referenced. The next instruction pushes the scalar on the stack using the BX base register and a stack segment override prefix (SS:) since the default would select the data segment for use with BX. The push instruction here would then typically be four bytes, or five bytes if a 16-bit displacement were needed.

The two vector arguments may either be vectors of scalars (1,2,4,8, or 10-bytes) or vectors of other data structures of arbitrary length. The 286 uses a special form of multiply instruction for indexing that disposes of the useless high-order half of the double-length product. Assuming an arbitrary vector element size, the reference code would be:

| MOV   | SI, i                          | <br>3-4 | bytes |

|-------|--------------------------------|---------|-------|

| BOUND | SI, static vector bounds       | <br>11  | 11    |

| IMUL  | SI, SI, static vector el size  | <br>H   | 11    |

| PUSH  | static vector[SI]              | <br>st  | ti    |

| MOV   | SI, j                          | <br>24  | 15    |

| BOUND | SI, dynamic vector bounds      | <br>11  | Ħ     |

| IMUL  | SI, SI, dynamic vector el size | <br>н   | n     |

| PUSH  | dynamic_vector[BP+SI]          | <br>II. | Ħ     |

The instructions are either three or four bytes depending on the displacement length (8 or 16-bits). If bounds checking is disabled, the sequence can be simplified to:

| IMUL | SI, i, static vector el size  | 4-6 bytes |

|------|-------------------------------|-----------|

| PUSH | static vector[SI] — —         | 3-4 bytes |

| IMUL | SI, j, dynamic vector el size | 4-6 bytes |

| PUSH | dynamic vector[BP+SI]         | 3-4 bytes |

The multiply instructions are 4-6 bytes depending on the length of the displacements and element sizes (8 or 16-bits). Note the use of double indexing plus displacement in the last example.

The reference code for static (global) or dynamic (local) record references is identical to that for the corresponding scalar references, since the compiler will fold the field offset into the record displacement during compilation. The reference code for the record field accessed via a pointer into an extra data segment (or heap, as it is sometimes called) is:

| · LES | BX, pointer  | load extra segment register/BX |

|-------|--------------|--------------------------------|

|       |              | with pointer                   |

| PUSH  | ES:field[BX] | reference field in record      |

The LES instruction is 3-4 bytes and the PUSH instruction is 4-5 bytes because of the ES override prefix.

# \*\* 4. COMPILATION TECHNIQUES FOR LOCAL CODE QUALITY \*\*

Design of a good code generator for the 286 microprocessor can use many of the general techniques described in the numerous texts (e.g.7) and articles (8,9,10) on this subject. Also many of the usual code improvement techniques such as common sub-expression elimination, dead code elimination, constant expression folding, strength reduction, variable subsumption, code motion, etc. can be applied with any target machine architecture. The reader is assumed to be familiar with these generic aspects of code generation and improvement, so the following discussion directs itself to 286-specific aspects of good code generation. Since generation of optional code sequences is computationally impractical (8), some heuristic approaches that seem particularly suited for the 286 are described.

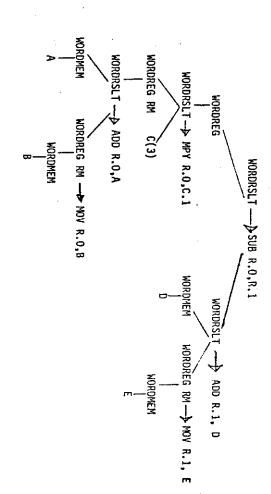

We assume the problem is to take as input a syntactically and semantically correct low-level intermediate representation of the source program, and convert it to 286 machine code in a particular object language format (e.g. Sec. 6). The sequence of intermediate form operators received as input is to be converted to an equivalent sequence of 286 machine operators. The mapping is in general many-to-many, since several intermediate operations may be performed in a single machine operation (e.g. a machine operation that performs complex address arithmetic for one of its operands), or conversely one complex intermediate operation may expand into several machine operations. Generation of a single machine instruction can be broken down into three steps:

- choice of instruction form ,

- allocation of registers,

- emission of instruction.

This section will present heuristic, but systematic, techniques for doing these three tasks for the iAPX 286 instruction set.

#### \*\* CHOICE OF INSTRUCTION FORM \*\*

The most natural and systematic method for translating context-free input from one form to another is that of syntax-directed translation (7). This approach is developed into a code generation technique by Glanville (11) and is likely to become the method of choice in new code generator designs. The 286-specific description given here is taken largely from an earlier paper (12) describing the Pascal-86 (13) code generator.

Assume previous compiler stages have performed lexical, syntactic, and semantic analysis of the program, inserted necessary type conversions, performed code improvements, and that the program is now represented as an abstract attributed parse tree. The tree nodes' attributes are the usual semantic attributes such as variable addresses, constant values, and so on. The control constructs (if-then-else,do-while, etc.) may be represented in high-level form (i.e. not broken down into labels and jumps), but we assume expressions and assignments are represented in the input tree as low-level machine types and operators. Code improvements as mentioned earlier are assumed to be logically separate from code generation. In particular common sub-expressions are eliminated by inserting an assignment statement into the program tree and replacing redundant computations of the common sub-expression with references to the assignment target.

The method for instruction form selection to be described here will take as input one entire assignment statement or expression subtree at a time and convert it into an equivalent "code tree" which will later be traversed to emit the actual instruction sequence.

We build the code tree bottom-up by parsing the prefix representation of the expression tree with a bottom-up parser. (Either top-down or bottom-up approaches may be used, but bottom-up allows the first pass of register allocation to proceed as a co-routine to instruction form selection, as will subsequently be shown.)

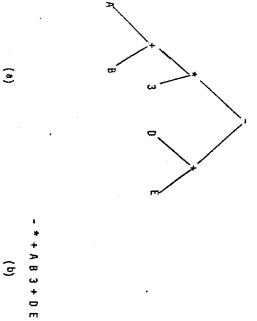

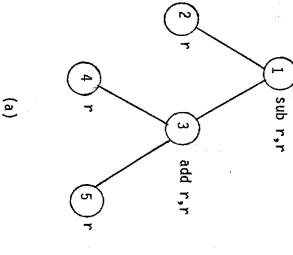

Figure 4.1 shows an expression tree (a), its prefix representation (b), and the equivalent code tree (c). The translation is performed by following the rules contained in the translation grammar of the form:

lhs ::= rhs ⇒ ins

where lhs is the left-hand side (typically a register non-terminal) rhs is the right-hand side (typically a subexpression) ins is the instruction to compute rhs into lhs, if any.

The translation grammar contains a rule for each instruction form, and non-terminals correspond to intermediate results stored in registers. The left-hand side non-terminal represents the location where the result of the right-hand side expression is computed. Non-terminals are represented in the rules by lower case names, while terminal symbols appear as upper-case names or quoted special symbols, for example:

wordreg.O ::= WORD\_SUB wordreg.O C.1 ⇒ SUB R.O, C.1

Application of this rule constructs a new register node in the code tree and associates it with the SUB instruction as an attribute. Other attributes associated with code tree nodes indicate register sets, constant values, and so forth. The .n suffix on grammar symbols indicate the actual associations among corresponding symbols in left-hand sides, right-hand sides, and instructions.

Another example is the rule:

wordreg.0 ::= WORD\_DEREF addr.1  $\Rightarrow$  MOV R.O, M.1

which loads a register from memory. Attributes of addr.1 include the address components of base register set, index register set, and displacement. Since the left-hand side register set is not associated with a right-hand side register set, the register allocator (to be described later) will allocate a register set to the result. Register sets indicate the set of possible registers that may actually be used in the final generated code.

9

FIGURE 4.1 (a) AN EXPRESSION TREE

(b) ITS PREFIX REPRESENTATION

(c) ITS EQUIVALENT CODE TREE

ට

Some things to keep in mind when designing the translation grammar are ambiguity, blocking, and cycles — the ABC's of code translation problems. Ambiguity tends to appear in the grammar because there is more than one instruction sequence to use for a given operation (e.g. 'SUB reg0, mem' or 'MOV reg1, mem; SUB reg0, regl). Blocking may occur if a necessary rule is missing from the grammar and the parser cannot proceed. Cycling may occur if a cycle of single productions (i.e. renamings) exist in the grammar (e.g. for coercing from one type to another). Occasionally a single-production introduced to cure a blocking problem may introduce a cycling problem.

Straighforward approaches in grammar design for code generation generally produce ambiguities. For example:

- wordreg.0 ::= wordmem.1 → MOV R.O, M.1

- (2) wordreg.0 ::= WORD SUB wordreg.0 wordreg.1 ⇒ SUB R.O. R.1

- (3) wordreg.0 ::= WORD SUB wordreg.0 wordmem.1 → SUB R.O. M.1

yields the ambiguity given in the preceeding paragraph where (1);(2) is equivalent to (3). It can be removed by creating a separate non-terminal to name only non-trivial (i.e. non-leaf) register values:

- wordreg.0 ::= wordmem.1  $\Longrightarrow$  MOV R.O, M.1

- wordrsIt.0 ::= WORD\_SUB wordreg.0 wordrsIt.1 ⇒ SUB R.O, R.1 wordrsIt.0 ::= WORD\_SUB wordreg.0 wordmem.1 ⇒ SUB R.O, M.1

- (4) wordreg.0 ::= wordrs1t.0

Here non-trivial register values are named "wordrslt" and may be coerced to "wordreg" values for use as lefthand operands by the single production in (4). Rule (2) is rewritten to accept only non-trivial register values for its right-hand operand. This removes the grammatical ambiguity in preference to the better (single instruction) sequence.

The full set of rules for binary operators in the 286 must take into account the nine terms in the cross-product

(mem, const, expr) X (mem, const, expr)

if it is to avoid blocking.

These nine terms are mapped onto three instruction forms: register-register (RR), register-memory (RM), and register-constant (RC). For <u>non-commutative</u> operators the left operand must be in a register, and the mapping is:

In transforming this mapping into a grammar, the first six products become loading rules leading to one of the last three products, which become computing rules.

For commutative operators the mapping is less restrictive:

The full set of rules for binary commutative and non-commutative operators ('cbop' and 'ncbop', respectively) are concisely summarized in five loading/renaming rules, three non-commutative binary computation rules, and five commutative binary computation rules, as shown in Table 4.1. The example in Figure 4.1(c) should now be fully comprehensible. Note that the rules in Table 4.1 will unambiguously: in the case of 'const x const' only load one of the constants; in a commutative 'const x mem' will load the memory operand; in a non-commutative 'const x mem' will load the constant operand; and so forth.

## loading/renaming

```

wordreg.0::= wordrslt.0

wordreg.0::= Cl → MOV R.O, C.1

wordreg.0::= wordmem.1 → MOV R.O, M.1

wordreg RM.0::= wordrslt.0

wordreg RM.0::= wordmem.1 → MOV R.O, M.1

```

## non-commutative binary computation

```

wordrslt.0::=ncbop.1 wordreg.0 C.2 \Longrightarrow OP.1 R.O, C.2 wordrslt.0::= ncbop.1 wordreg.0 wordmem.2 \Longrightarrow OP.1 R.O, M.2 wordrslt.0::= ncbop.1 wordreg.0 wordrslt.2 \Longrightarrow OP.1 R.O, R.2

```

# commutative binary computation

```

wordrslt.0::= cbop.1 wordrslt.0 wordmem.2 \Rightarrow OP.1 R.O, M.2 wordrslt.0::= cbop.1 wordrslt.0 wordrslt.2 \Rightarrow OP.1 R.O, R.2 wordrslt.0::= cbop.1 wordmem.2 wordregRM.0 \Rightarrow OP.1 R.O, M.2 wordrslt.0::= cbop.1 wordregRM.0 C.2 \Rightarrow OP.1 R.O, C.2 wordrslt.0::= cbop.1 C.1 wordreg.0 \Rightarrow OP.1 R.O, C.1

```

TABLE 4.1 BINARY OPERATION TRANSLATION RULES

Allocation of registers is inter-related with choice of instruction forms, and logically these two operations are viewed as co-routines. One easy method to decouple the two is to assume an unlimited number of registers of each type, during instruction form selection, and then to insert register loads, stores, or moves where necessary, during register allocation and assignment. For our purposes we will allocate registers to a single code tree at a time, and actually make three passes over the code tree: (1) bottom-up as the tree (see Fig. 4.1c) is being built by the parser-driver instruction form selector, (2) top-down in a subsequent pass, and (3) bottom-up while emitting instructions. The second and third passes over the tree will actually occur in a single tree traversal utilizing both a prefix (i.e. top-down) and a postfix (i.e. bottom-up) visit to each node.

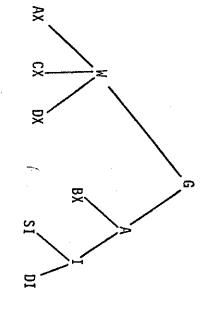

Figure 4.2 shows the register set for the iAPX 286, and clearly many of these registers have fixed purposes and are unavailable for allocation. In particular, BP and SP among the generic data registers denote the local stack frame and the stacktop, respectively. The other generic data registers may be allocated, however their usage is not fully general, and some care is required in their allocation. The usual simple schemes (e.g. 7) applicable to machines with general register organizations are inappropriate to the 286, while the more powerful graph coloring approach (14) provides a useful model although not a useful algorithm in this case.

Figure 4.3 shows a more realistic view of the allocatable registers within the 286, showing them in tree form as a nested hierarchy of register classes. The G (generic) class contains the W (working) and A (address) classes. The W class consists of the AX, CX, and DX registers, while the A class consists of the BX register and the I (index) class, the latter containing the SI and DI registers. For example a register-to-register add instruction requires two G-registers, a string operation needs the two I-registers, a doubly-indexed reference needs the BX-register and one I-register, byte operations use the W-registers, and so forth. The representation in Figure 4.3 is not optimal (BX should be either a W- or A-register, for instance), but it is practical, as will be shown.

Now, in the textbook allocation algorithm (7) for a general register machine, the code tree nodes would each contain a single integer attribute (sometimes called the Sethi-Ullman number (15) ) specifying the number of registers needed to evaluate the node. Clearly this is a synthesized (i.e. derived bottom-up) attribute set on the first pass (up) the code tree. We do the analagous function, but instead of using a single integer, we use an integer vector that represents the number of registers required from each class, including the singleton classes composed of one specific register each. We call this a <u>class vector</u>, and it represents the number of registers needed in each class (but not more specific classes, i.e. it is non-cumulative). An arbitrary order for the elements of the vector might be [AX, CX, DX, BX, SI, DI, W,I,A,G]. Then the vector [1,0,0,0,0,0,0,0,1,1], for example, indicates three registers: AX, one address register, and one other generic register. The components of a given vector, X, are referenced as X.AX, X.BX, X.I, etc. and in our example X.AX, X.A, and X.G are all one, while all other components are zero. A more readable way of writing the vector [1,0,0,0,0,0,0,0,1,1] is as [AX,A(1),G(1)], and we will follow this convention. Note that our representation is not unique, since, for example, [BX,I(2)], [BX,SI,I(1)] and [A(3)] are three equivalent representations of the three address registers. This will not affect the allocation.

Figure 4.2: iAPX 286 register set

FIGURE 4.3 iAPX 286 REGISTER CLASS HIERARCHY

For any given class vectors, X and Y define the operations:

ii) X v Y:

the cardinality of X, equal to the sum of the elements of X; the "minimax" join of X and Y, defined as the class vector Z with minimum cardinality but maximum generality (i.e. registers placed at highest possible levels in the hierarchy), such that either X or Y could be allocated from Z, examples:

```

[AX,W(1)] v [CX,W(1)] = [AX,CX]

[W(1)] \times [A(1)] = [W(1), A(1)]

[AX] v [W(1),G(1)] = [AX,G(1)]

```

algorithm:

Z.r:=max(X.r, Y.r), for  $r \in [AX,CX,DX,BX,SI,DI]$  $Z.W:=\max(0,\max(X.W+Xw, Y.W+Yw)-Zw);$  $Z.I:=\max(0, \max(X.I+Xi,Y.I+Yi)-Zi);$  $Z.A:=\max(0,\max(X.A+Xa,Y.A+Ya)-Za);$

$Z.G:=\max(0,\max(X.G+Xq,Y.G+Yq)-Zq);$

where for R any of the X,Y,or Z we define

Rw = R.AX+R.CX+R.DX;

Ri = R.SI+R.DI;Ra = R.BX+Ri+R.I:

Rg = Rw+R.W+Ra+R.A:

iii) X ? Y:

the non-interference predicate, true if registers can be assigned disjointly to X and Y, false otherwise; examples:

[AX] ? [W(2)] = true[W(2)] ? [W(2)] = false

[G(4)] ? [W(3)] = false

algorithm: true if X.r + Y.r ≠ 2 for r ∈ [AX,CX,DX,BX,SI,DI]

and  $X.W+Xw+Y.W+Yw \leq 3$ and  $X.I+Xi+Y.I+Yi \le 2$

and  $X.A+Xa+Y.A+Ya \leq 3$

and  $X.G+Xg+Y.G+Yg \le 6$

iv) X + Y

the vector sum of X and Y, defined only if X ? Y holds, and equal to the class vector Z defined simply as the element-wise sum of class vectors X and Y; examples:

[AX]+[W(2)] = [AX,W(2)] $[W(\bar{1}),I(1)] + [W(\bar{1}),I(\bar{1})] = [W(2),I(2)]$ [AX]+[AX] = undefined, due to interference in AX. the <u>restriction</u> of X to Y, being a class vector, X', such that each register represented in X is also represented in X' and in Y at as general a level as X and Y will permit; in general, more than one restriction is possible and the implemented algorithm arbitrarily defines a choice among them; in our usage we will consider the restriction to have <u>failed</u> if |X|>|X'|; examples:

[AX]/[BX] = [ ] (failed)

[AX]/[W(2)] = [AX]

match(G);

match(s);

[AX]/[BX] = [ ] (failed)

[AX]/[W(2)] = [AX]

[BX]/[AX,CX,BX] = [BX]

[G(1)]/[AX,CX,BX] = [AX] (or [CX] or [BX]);

[A(2)]/[G(1),I(1)] = [A(1),I(1)]

algorithm:

create a temporary class vector called 'balance' (which will contain the "bank balance", either positive or negative number of registers, at each level of the hierarchy); treat each class vector as though it were the tree of Fig. 4.3

adj(s,G) for  $s \in (W,A)$

```

match(r); adj(r,W), adj(r,G) for r \in (AX,CX,DX)

match(s); adj(s,A), adj(s,G) for se(BX,I)

match(n); adj(r,I), adj(r,A), adj(r,G) for

r∈(SI,DI)

where:

match(s) is:

X.s:= min(X.s,Y.s);

balance.s:= Y.s-X.s;

and

adj(s,s') is (in guarded command form);

balance.s < 0 and

balance.s'> 0 ⇒

increment (balance.s);

decrement (balance.s');

increment (X.s);

| balance.s > 0 and

balance.s' < 0 \Rightarrow

decrement (balance.s);

increment (balance.s');

increment (X'.s);

lod

```

Note:

the order of execution of the algorithm for vector elements at the same hierarchy level arbitrarily chooses among the family of possible results.

Given these operations it is now possible to define register allocation and register assignment as algorithms employing sequences of these fundamental operations. As already mentioned, three passes over the code tree (build by the parser driven instruction form selector) are performed. The first, bottom-up, pass occurs as the tree is built and basically computes the class vectors as synthesized attributes of the tree. The second, top-down, pass sets the target path (16) as an inherited attribute from higher-level to lower-level nodes on the way down the code tree. The third, bottom-up, pass will then emit instructions (using a template mechanism, to be described). This can be expressed (in guarded command form) as:

od

Each of these operations will now be explained:

### "BUILD CODE TREE AND COMPUTE CLASS VECTORS"

This operation involves the parser driven instruction form selector and the register allocator as coroutines. A code tree is composed of the operators and operands for a single expression. This first pass can be expressed as:

<u>do</u>

→ end of expression ⇒ build node (root, left, right)

match targets to preferences

choose evaluation order

choose target path

od

1

The 'build node' routine is performed by the instruction form selector which selects a machine operator and installs it as the 'root' node for the operation, with associated 'left' and 'right' operand subtrees. Instruction form selection has already been described and the tree building is a simple utility operation.

Once the new node is entered in the code tree, it is necessary to match the possible target registers of its operand subtrees with the operand location preferences of the new operator. For example the result of a sub-computation may need to be placed in an index register in order to be used in an indexed address.

The algorithm is:

```

"Match targets to preferences"

```

```

for operand:= left, right ⇒

if root expects operand in a register ⇒

operand.target:= operand.target/root.operand.preference;

if |operand.target| = 0 "failed" ⇒

insert reg-reg move (operand, root)

fi

fi

rof

```

Simply stated, the subtree target registers are restricted to the root's operand location preferences. Failing this, a register-to-register move is inserted from the subtree target vector to the root preference vector. For example a multiply instruction could not restrict its target to the I class, but would have to use a move instruction from the AX register target to the I class register preference.

Choosing an evaluation order is important to efficient expression evaluation since it may determine whether or not registers must be "spilled" to memory during the course of evaluation. The general approach is to evaluate the more complex (register consuming) subtree first, so that it would have the most registers available to it. Hopefully then the less complex subtree can be entirely computed in the remaining registers not occupied by the first subtree's result. The algorithm to choose an evaluation order has several stages. The first is:

"choose evaluation order - Stage 1"

left.usage := left.subuse v (left.target + left.work);

right.usage := right.subuse v (right.target + right.work);

left.may\_be\_first := left.target ? right.usage;

right.may\_be\_first := right.target ? left.usage;

This simple sequence computes each operand's 'usage'vector as the join of its subtree's usage vector, 'subuse', and the sum of its 'target' and 'work' vectors. A work vector consists of working registers used in complex macro instructions or of registers clobbered as a side effect of the computation (e.g. DX in multiply or divide). Of course target and work vectors do not interfere. An operand 'may be first' in evaluation order if its target vector does not interfere with its companion's usage vector.

### "choose evaluation order - stage 2"

```

| left.may be first and ¬right.may be first ⇒ root.order:= left_first

| ¬ left.may be first and right.may be first ⇒ root.order:= right_first

| ¬ left.may be first and ¬ right.may be first ⇒ "must spill"

| root.order := right_first; spill(right)

```

### fi

This simply checks the cases: 1) both orders possible implies use the order with the lowest register usage; 2) either order possible implies use that order; 3) neither order possible implies spill an operand to memory. This is the classic textbook algorithm (7).

## "choose evaluation order - stage 3"

### fi

This establishes the root subusage depending on the order of evaluation and additionally defines an 'interference' vector for the first operand that is the join of the usage vector of the second operand with the work vector of the root. Notice that the first operand target vector need not be included in the second operand interference vector since these registers will already be marked as assigned when it is time to assign registers to the second target vector. Interference vectors are used by register assignment (in the later pass) in actually making assignments from the target vector while avoiding registers in the interference vector. For example the first operand may target [W(1)] while the second operand may use [AX]. Register assignment will assign a work register other than AX.

[Digression: The graph coloring approach to register allocation (14) actually constructs an interference graph. This is a graph in which nodes represent expression operands and arcs represent interferences, i.e. the two operands joined by an arc may not occupy the same register. Register assignment is a "coloring" of the graph where each color represents one of the machine registers and no two nodes connected by an arc may be the same color. Figure 4.4 gives a code tree and its corresponding interference graph. The basic rules are that (a) sibling targets interfere, (b) first operand targets interfere with second operand usages, and (c) non-commutative operation results interfere with their second operand target. The interference vectors constructed in the first pass handle interference types (a) and (b), while first pass target path selection handles type (c) interferences in our approach. End of digression.]

The only remaining operation in the first pass, assuming the root lies on the target path, is to choose a target path, i.e. which of the operand result targets should become the root result target. In the case of a commutative operator, the operand target with the largest cardinality is chosen for the root target:

"choose target path"

if root.path\_continues ⇒

if root.commutative and |left.target| < |right.target| ⇒

exchange (left,right,root)

fi

root.target := left.target; root.interference := left.interference

<u>fi</u>

green

) blue

) green

blue

) red

(b)

"red-R0, blue-R1, green-R2"

add R1, R0 sub R2, R1

(c)

FIGURE 4.4 a) CODE TREE

b) CORRESPONDING INTERFERENCE GRAPH

AND A VALID COLORING

c) AN ASSOCIATION OF REGISTERS TO COLORS

#### \*\* THE SECOND PASS \*\*

The second, top-down, pass is a good deal simpler than the first pass. In the first pass the bottom-up matching of target and preference vectors had generally refined the target vectors to more specific registers. This information (target and interference vectors) must now be passed back down the code tree along the target paths to the leaves, where the registers actually get loaded. Not all machine operations continue the target path (e.g. comparisons or moves), so the 'path continues' Boolean attribute is specified for each machine operation. The inheritance of target paths and emission of instructions is a top-down traversal of the code tree, passing down the target and interference vectors on the preorder visit to each interior node, and emitting the instruction on the postorder visit. It is defined recursively as follows:

"set target paths and emit instructions"

set\_and\_emit (code\_tree.root)

where we define it as:

"set and emit (n: code tree node)"

The actual instruction emission is defined as:

"emit instruction (n: code tree node)"

This algorithm treats three separate cases. In the first case, for an interior node that continues the target path, the target vector is passed up from the left (target path) operand, and the right operand target is freed. In the second case, for an interior node that breaks the target path, work registers are assigned, both operand target vectors are freed and the new target assigned. Finally, for the leaf node case, the new target is simply assigned. Following this the code pattern is emitted using a template expansion technique (17), and the work registers are freed.

Assigning and freeing registers uses the same basic class vector operations as the other register selection routines. The set of free registers, 'free set', is maintained as a class vector all of whose elements are specific (singleton class) registers. Note that the previous register allocation operations have allocated possibly non-specific registers to the various target sets and verified that they do not necessarily conflict with the corresponding interference sets. Therefore register assignment is guaranteed to find a specific target vector such that:

(i) | target/free set| = | target|

(ii) target ? interference holds.

This means there is absolutely no "on the fly" spilling of registers during register assignment; all essential spills were performed earlier, during the choice of an evaluation order for each operator's operands. This is called a "pre-planning" strategy in the literature (9).

It would be nice if we could just set target to be target/free set, but since there is more than one possible restriction of the target vector to the free set (some of which may conflict with the interference set) we must plod through, trying a register at a time:

"assign regs (target, interference)"

The class vector difference operator, -, used here is of course element-wise subtraction. This algorithm just tries the free registers one at a time and joins any that satisfy the criteria into the target set, thus making that register entry specific. (The bottom-up character of the join operator guarantees that once a specific register has geen assigned to the target vector, we will never have to back up and try another assignment.) The companion routine to free registers is of course:

"free regs (target)"

free-set := free\_set + target

### \*\* INSTRUCTION EMISSION \*\*

A table-driven, code template mechanism (17) is best used with the 286 to organize the mass of detail associated with actually emitting the instruction once the machine operator and registers have been chosen. It would handle such details as:

- the size of the displacement used to reference a memory operand;

- the size of any immediate operands;

- special instruction forms that may be useable because of the register involved (often the case with AX);

- management of the current stack frame size and its high water mark;

management of the current code segment size;

- association of compiler-generated labels with code segment offsets;

- association of the current condition code setting with the responsible instruction;

- management of jump and call displacements (i.e. span-dependent instructions);

- assembly of the instruction itself into the appropriate bit pattern with opcode, register, mode, displacement, etc. fields.

Each machine operator would have an associated table entry that would contain fields that are interpreted by the "template expander" to manage the myriad details listed above and emit the actual instruction patterns.

Techniques (18,19) exist for generating near optimal code for span-dependant instructions (such as jumps or calls), since this is in general an NP-complete problem. One simple technique is to just use a buffer capable of holding the equivalent of 127 bytes of generated 286 code. This can be used to resolve forward jumps into either short or long form: into short form if the jump target is in the buffer, into long form otherwise. This technique associates worst-case displacements (assuming all long jumps and calls) with the compiler-generated labels, so it may sometimes use a long form where a short form could be used. This is generally not significant, but one or more optimizing passes could be added to iteratively reduce the program to its optimal form, and usually a second iteration is sufficient.

#### \* EXAMPLES \*

Let's tackle some expamples now that show most of the register allocation mechanism in action. We'll use the assignment:

$$A[I]:= (B+C*D) - (E/F+G[J*K])$$

(Example 1)

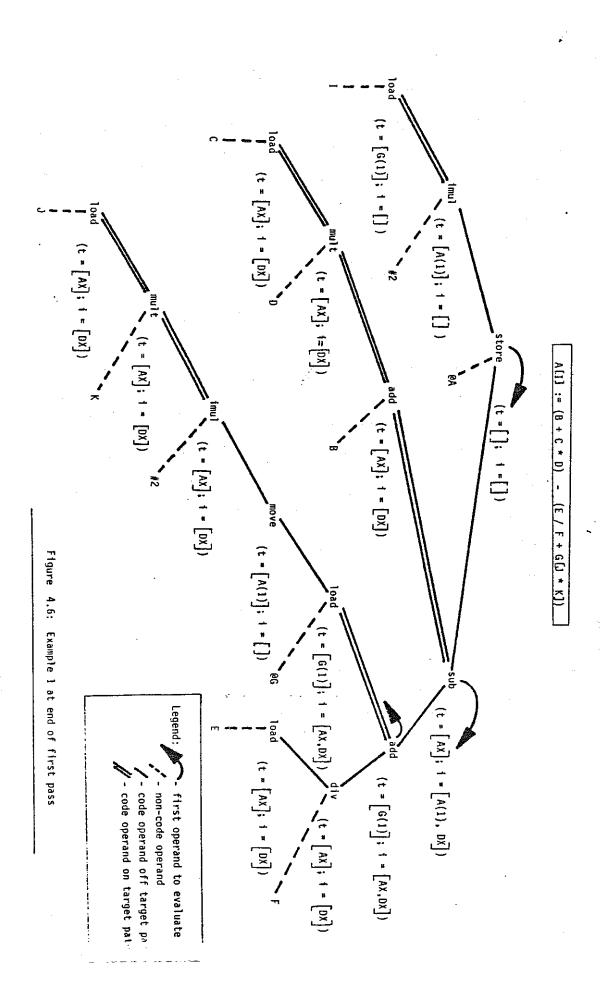

for our first example, and walk through the first (bottom-up) pass that builds the code tree. This code tree building is directed by the parser-driven instruction form selector described earlier. As it specifies each Node, the register allocation attributes are computed according to the previously given algorithms, which are summarized in terser notation in Figure 4.5. We will use this notation as we step through the construction of the code tree as driven by the bottom-up parser.

```

NOTATION:

n. . . . the new (parent) node

c. . . . any of its child nodes

t. . . . target

s. . . subuse

w. . . work

. . . interference

p. . . . preference for child c

cl... the left child

cr. . . . the right child

cl. . . . the child to be evaluated first *

c2. . . . the child to be evaluated second *

o. . . . evaluation order

path... path continues predicate

*Note: Evaluation order (c1, c2) is orthogonal to

**Note: The c subscript may be

conceptual operand order (cl, cr). For

omitted when the child

commutative operators, operand order may be

is understood.

reversed if |cl.t| > |cr.t| , changing the

target path.

```

### ATTRIBUTE COMPUTATION:

Figure 4.5: First-pass register allocation attribute computation.

(Initial attribute values are a function of the instruction operator (a constant table lookup), and computed attribute values are the result of the computation of Figure 4.5.)

```

NODE 1:

load

(A[I]:= (B+C*D) - (E/F+G[J*K]))

initially:

n.t=[G(1)]; n.w=[]; n.i=[]

n.s := [ ];

compute:

NODE 2:

imul

(A[I]:=(B+C*D) - (E/F+G[J*K]) )

node 1

#2 (constant)

initially:

compute:

NODE 3:

(A[I]:=(B+C*D) - E/F+G[J*K])

load

n.t=[G(1)]; n.w=n.i=[]

n.s := [];

initially:

compute:

NODE 4:

mult

(A[I]:=(B+C*D) - (E/F+G[J*K]))

node 3

n.t=[AX]; n.w=[DX]; n.p=[AX]; n.i=[]

initially:

compute:

c.t := [AX]; c.u := [AX];

n.s := [AX]; c.i := [DX];

n.t := [AX]: n.i := [DX];

NODE 5:

add

(A[I]:=(B+C*D) - E/F+G[J*K])

node 4

initially:

n.t=n.p=[G(1)]; n.w=n.i=[ ]

compute:

c.t := [AX]; c.u := [AX,DX];

n.s := [AX,DX]; c.i := [DX];

n.t := [AX]; n.i := [DX];

NODE 6:

load

(A[I]:=(B+C*D) - (E/F+G[J*K]))

initially:

n.t=[G(1)]; n.w=n.i=[ ]

compute:

n.s:= [ ];

```

```

NODE 7:

(A[I]:=(B+C*D) - (E/F+G[J*K]))

node 6

n.t=n.p=[AX]; n.w=[DX];n.i=[ ]

initially:

c.t := [AX]; c.u := [AX];

n.s := [AX]; c.i := [DX];

compute:

n.t := [AX]; n.i := [DX];

NODE 8:

(A[I]:=(B+C*D) - (E/F+G[J*K]))

load

initially:

n.t=[G(1)]; n.w=n.i=[]

compute:

n.s := [ ];

NODE 9:

(A[I]:=(B=C*D) - (E/F+G[J*K]))

mult

node 8

n.p=n.t=[AX]; n.w=[DX]; n.i=[ ]

initially:

compute:

c.t := [AX]; c.u := [AX];

n.s := [AX]; c.i := [DX];

n.t := [AX]; n.i := [DX];

NODE 10: imul

(A[I]:=(B+C*D) - E/F+G[J*K])

node 9

initially:

n.p=n.t=[G(1)]; n.w=n.i=[

compute:

c.t := [AX]; c.u := [AX,DX];

n.s := [AX,DX]; c.i := [DX];

n.t := [AX]; n.i := [DX];

NODE 11: load

(A[I]:=(B+C*D) - (E/F+G[J*K]))

node 10

0G

n.p=[A(1)]; n.t=[G(1)]; n.w=n.i=[]

initially:

c.t := [ ];

compute:

*** restriction exception:

target and preference incompatible -- insert move ***

NODE 11' : move

node 10

initially:

n.p=n.t=[G(1)]; n.w=n.i=[ ]

compute:

c.t := [AX]; c.u := [AX,DX];

n.s := [AX,DX]; c.i:= [DX];

```

```

NODE 11: load

(cont'd) /

node 11'

c.t := [A(1)]; c.u := [A(1),AX,DX];

compute:

n.s := [A(1),AX,DX]; c.i := [];

NODE 12: add

(A[1]:=(B+C*D) - (E/F+G[J*K]))

node 7 node 11

n.p<sub>[</sub>=n.p<sub>r</sub>=n.t=[G(1)]; n.w=n.i=[]

initially:

cl.t := [AX]; cl.u := [AX,DX];

compute:

cr.t := [G(1)]; cr.u := [A(1),AX,DX];

n.o := right first;

n.s := [A(1),AX,DX];

c1.i := [AX,DX]; c2.i := [DX];

|cr.t| > |cl.t| \Rightarrow swap (l,r);

n.t := [G(1)]; n.i := [];

NODE 13: sub

(A[I]:=(B+C*D) - (E/F+G[J*K]))

node 5 node 12

n.p<sub>i</sub>=n.p<sub>i</sub>=n.t=[G(1)]; n.w=n.i=[]

cl.t :=[AX]; cl.u := [AX,DX];

initially:

compute:

cr.t := [G(1)]; cr.u := [A(1),AX,DX];

n.o := right first;

n.s := [A(1),AX,DX];

c1.i := [AX,DX]; c2.i := [DX];

n.t := [AX]; n.i := [DX];

NODE 14: store

(A[I]:=(B+C*D) - (E/F+G[J*K]))

node 2 @A

node 13

n.p_l = [A(1)]; n.p_r = [G(1)]; n.t = n.w = n.i = []

initially:

cl.t :=[A(1)]; cl.u := [A(1)];

compute:

cr.t := [AX]; cr.u := [A(1),AX,DX];

n.o := right first;

n.s := [A(1),AX,DX];

c1.i:= [A(1),DX]; c2.i := [];

```

Figure 4.6 shows the code tree at completion of pass 1 as just performed, with target and interference vectors specified, order of evaluation shown, and target paths marked. Note that order of evaluation is orthogonal to target path selection, that a move was inserted between the "J\*K" subscript computation and the loading of G[J\*K], and that no spills were necessary.

In the second, top-down, pass we merely pass target and interference vectors down target paths. In Figure 4.6, only the leftmost target path inheritance results in a change, with the 'load (I)' node changing its target vector from '[G(1)]' to '[A(1)]'. Finally on the third, bottom-up, pass we assign specific registers based on the previous allocation and call the template expander. The sequence of templates based on Figure 4.6 and the given register assignment algorithm would be (again with target operands on the left):

|            | load  | AX,J     |

|------------|-------|----------|

|            | mult  | AX,K     |

|            | imul  | AX,#2    |

|            | move  | BX,AX    |

| (1)        | load  | BX,G[BX] |

| (1)<br>(2) | load  | AX,E     |

| (3)        | div   | AX,F     |

| •          | add   | BX,AX    |

|            | load  | AX,C     |

|            | mult- | AX,D     |

|            | add   | AX,B     |

|            | sub   | AX,BX    |

| (4)        | load  | BX,I     |

|            | imul  | BX,#2    |

|            | store | A[BX],AX |

The entire assignment (A[I]:=(B+C\*D)-(E/F+G[J\*K])) is thus computed using only three registers (AX, DX, BX). Note that DX does not appear above, as it is a work register for the double length dividend or product in divides or multiplies. In particular, the template expander will need to propagate the sign of the dividend through DX prior to the division of lines (2) and (3). This may result in DX actually being loaded in line (2) and then getting shifted arithmetically into AX prior to the division in line (3); this is one of the nuisance details handled by the code template mechanism. Note also that in lines (1) and (4) we have arbitrarily chosen BX as the target register, when our target vector was actually more general. This is only to indicate that BX could be chosen if the other registers were needed, and that this assignment could be restrained to three registers. In general, however, the assignment will be "loose" in the sense that if there is not much "pressure" on the registers, an arbitrary selection will be made that may harmlessly employ more registers than the minimum possible. A simple heuristic to select the most recently used registers could be employed if global register minimization is desired, but this is not worth the effort, as a rule, on the iAPX 286. One heuristic that is valuable is to track current register contents inside the register assignment procedure and eliminate register loads wherever possible, or at least convert them into register moves.

# \*\* A SECOND EXAMPLE \*\*

Since our first example did not generate any spills, we now give a simple example of the spill mechanism, using the expression:

```

A*B + C/D

NODE 1:

load

n.t=[G(1)]; n.w=n.i=[]

initially:

compute:

n.s=[]

node 2:

mult

initially:

n.p=n.t=[AX]; n.w=[DX]; n.i=[]

c.t := [AX]; c.u := [AX];

n.s := [AX]; c.i := [DX];

compute:

node 1

n.t:= [AX]; n.i:=[DX];

node 3:

load

initially:

n.t=[G(1)]; n.w=n.i=[]

compute:

n.s:=[];

node 4:

div

initially:

n.p=n.t=[AX]; n.w=[DX]; n.i=[]

c.t:=[AX]; c.u:=[AX];

compute: -

n.s:=[AX]; c.i:=[DX];

node 3

n.t:=[AX]; n.i:=[DX];

n.p<sub>1</sub> =n.p<sub>y</sub> =n.t=[G(1)]; n.w=n.i=[]

c1.t:=[AX]; c1.u:=[AX,DX];

node 5:

add

initially:

compute:

cr.t:=[AX]; cr.u:=[AX,DX];

node 4

r.o *** order conflict - spill one ***

node 2

node 4':

spill

initially:

n.p=n.t=[G(1)]; n.w=n.i=[]

c.t:=[AX]; c.u:=[AX,DX];

compute:

n.s:=[AX,DX]; c.i:=[DX];

node 4

node 5:

add

n.o:=right first;

compute:

(cont'd)/

cr.t:=[G(1)]; cr.u:=[AX,DX];

cl.i:=[AX,ĎX]; c2.i:=[DX];

|cr.tl>|c].t|⇒ swap(l,r);

node 4'

node -2

```

Now the spill macro that is inserted as node 4' may be handled in two ways, as:

- i) a move from a register in the target vector to another register in the preference vector, if this would remove the order conflict (i.e.  $(n.p_1?cr.u)$  or  $(n.p_n?cl.u)$  holds); or as

- ii) a spill to a temporary storage location (e.g. the stack) and a change of the parent node to reference the operand in memory, if possible, or to reload the operand, if it must be in a register;

In our example the first alternative is preferable and leads to:

load AX,C

mult AX,D

move CX,AX

load AX,A

mult AX,B

add AX,CX

The second alternative would be less desireable, as

load AX,C

mult AX,D

push AX

load AX,A

mult AX,B

add AX,temp - or - pop DX

add AX,DX

# \* A TECHNIQUE FOR LARGE DATA STRUCTURES \*

The segmentation facilities of the iAPX 286 are useful in structuring large address spaces into conceptually manageable units. The four segment registers (CS, DS, SS, ES) treat the current code, data, stack, and external areas as logically separate segments of memory whose relative position in a linear physical memory is immaterial. Whenever possible it is desireable to modularize data structures so that they can be conveniently referenced by this segmentation scheme. Occasionally, though, a natural decomposition of a large (> 64 KBytes) data structure does not exist, and it must be treated in its entirety. Examples might be large tables or matrices such as used in some control or numeric applications. This section discusses a compilation approach to large data structures that cannot entirely reside in a single segment.

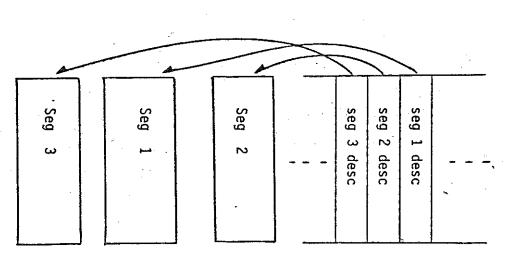

Figure 4.7 shows the situation for a multi-segment data structure, with a contiguous portion of a segment table (GDT or LDT) containing the segment descriptors for the segments composing the structure. For arrays, the segments should always contain an integral number of array elements (i.e. not split an element across segment boundaries). For efficiency in manipulating arrays, the number of elements in a segment could be a power of two, so that shifts instead of divides could be used; this is not mandatory. For example, an 80,000 element array of two-byte integers would appear as two segments of  $2^{15}$  =32,768 elements, followed by a segment of 14,464 elements. As another example, an 80,000 element array of three-byte entries would appear as four segments of  $2^{14}$  =16,384 elements, followed by a segment of 14,464 elements; the first four segments are each 49,152 bytes in length. The largest power of two is used that will still yield an array slice that fits into 64 Kbytes.

Segment table:

Figure 4.7: Multi-segment data structure

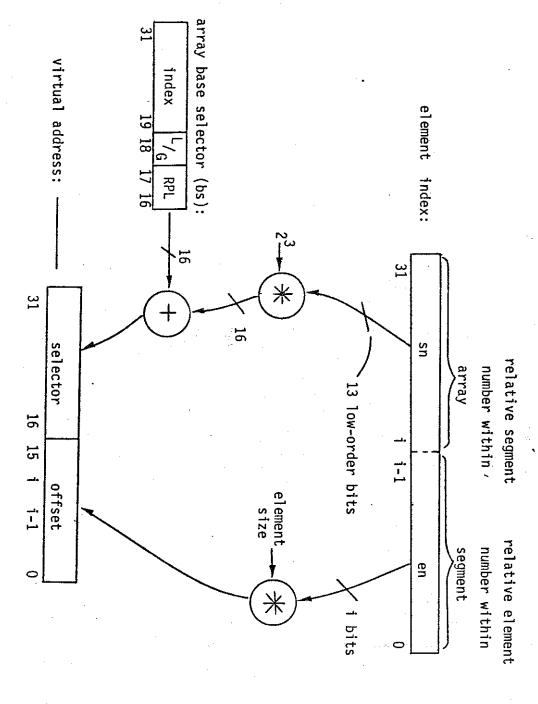

Figure 4.8 shows the general case address computation for a multi-segment data structure. A linear 32-bit element index is viewed at the top of the figure as a relative segment number, sn, followed by a relative element number, en, within the segment. The significant bits (up to 13) of sn are shifted left by 3 bit positions (to clear the L/G and RPL fields of the selector), added to the base selector value, and taken as the selector portion of the array element virtual address. The en value is multiplied by the element size and used as the offset portion of the array element virtual address. Assuming an index computation has left the element index in DX:AX, we have:

-- DX:AX contains element index

-- array element virtual address in ES:BX

where i is the number of bits within en. In the special case where i=16, such as for a byte string or byte array, the above reduces to:

| mov | BX,AX |

|-----|-------|

| sh1 | DX,3  |

| add | DX,bs |

| mov | ES.DX |

Figure 4.8: Multi-segment address computation (general case)

# \*\* 5. EXCEPTIONS, ERRORS, DEBUGGING, AND INTERPRETATION \*\*

Handling of exceptional conditions and errors, and debugging of programs are important topics in programming language implementation. In the iAPX 286 all exceptional conditions are intercepted by vectoring through the interrupt descriptor table (IDT) to a procedure or task that handles the exception. The IDT entries are either interrupt trap gates (for procedure handlers) or task gates (for task handlers). A procedure handler executes as a simple interrupt procedure within the current task and is often a part of the operating system portion of the virtual address space. A task handler is an entirely separate task for servicing of interrupts that can use its own local address space. Most exceptions are maskable, in that they will only be honored by the processor if the interrupt enable bit (IF) in the flags register is set. Interrupts are automatically disabled by transfer to a procedure handler, but transfer to a task handler loads the flags register from the new task state segment, setting IF as determined in the new TSS.

Three classes of events may cause an exception handler to be invoked:

- external interrupts that assert a signal on the processor's interrupt pins,

- traps caused by the software interrupt instructions, and faults detected before or during instruction execution.

External interrupts normally proceed from an 8259A interrupt controller that resolves priorities among interrupt sources and provides an interrupt address. Traps are casued explicitly by the INT(#) instruction that uses the number (#) as an index into the interrupt descriptor table. A one-byte form of the instruction implicitly uses IDT index 3 and can be used by debuggers for setting breakpoints. Faults detected before or during instruction execution cause automatic transfer of control through the IDT and in general are not masked (i.e. do not depend on the setting of IF). Figure 5.1 shows the pre-assigned and reserved IDT entries. An asterisk indicates a non-maskable fault. Note that entry 1, the single-step trap, is listed as non-maskable because it is controlled by the trap flag, TF, rather than the interrupt enable flag, IF. Also note that entry 2, the non-maskable interrupt, is triggered by a signal on the processor's NMI pin. Non-maskable faults have a higher priority than external interrupts and are handled first.

The interrupt mechanism for protection violations will store an interrupt error word on the stack of the interrupt error handler - this is described in detail in the appropriate 286 manual (2). Note that a debugger would typically want to field protection violations during a debug session and the underlying operating system needs to support this requirement.

Processor extensions, or coprocessors, provide their own error codes through status inquiry instructions of the coprocessor. The 286 merely provides a generic trap (#16) for these conditions.

| IDT no.                               | Exception                                                                                                                                |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 0*<br>1*<br>2*<br>3<br>4*<br>5*<br>6* | divide error single-step non-maskable interrupt breakpoint trap INTO-detected integer overflow BOUND-detected range error invalid opcode |

| 7*<br>8*                              | processor extension (coprocessor) not present double protection fault                                                                    |

| 9*<br>10*<br>11*<br>12*<br>13*        | Processor extension (coprocessor) segment overrun invalid task segment format segment not present stack under/over flow                  |

| 14-15<br>16<br>17-31                  | general protection violation reserved processor extension (coprocessor) detected fault reserved                                          |

\*- non-maskable

Figure 5.1: IDT pre-assigned and reserved entries.

#### \* DEBUGGERS \*

Debuggers are generally of two varieties - system debuggers and application debuggers. System debuggers are either low-level monitor-style debuggers at the machine level, or intelligent debuggers that understand and recognize operating system data structures and descriptor tables. System debuggers are in some ways simpler than application debuggers, since they can assume they control the entire system during a debug session, and in other ways more complex, since they must deal with operating system data structures, descriptor tables, and multi-tasking.

Application debuggers also come in two varieties - assembly level, or high-level language level. Either way an application debugger must assume the existence of an underlying operating system and of other applications programs, none of which may have their integrity violated. Indeed multiple instances of an application debugger may be in use simultaneously. Whether an application debugger needs to support debugging of multitasking applications is determined by the situation, but typically they do not.

Debuggers in the iAPX 286 may insert breakpoints using the one-byte form of the INT instruction. Single-stepping is also possible by setting the TF flag, but it is recommended only for machine-level debugging, as typically a high-level language programmer views the statement or even the procedure as a single "step". With a table of statement and procedure entry offsets, breakpoints may be inserted to give the high-level language equivalent of single stepping. Typically such a table is established as a "breakpoint table" with entries such as:

ENTRY: code seg offset breakpoint byte

Initially a breakpoint table is established for each code segment where breakpoints will be set, and the initial value of the breakpoint byte is set to the one-byte INT opcode. The following instructions would set/clear all the breakpoints in a breakpoint table (such as might be done for single statement stepping if the table is of statement offsets):

```

let bpt=breakpoint table description: (table

table

code)

(address.

lenath.

offset=code segment offset field of entry

bpop=breakpoint opcode (immediate value)

bb=breakpoint byte field of entry

bb swap:

mov

SI.bpt

CX.bpt+2

number of entries

mov

mov

ES,bpt+4

segment base

DI, [SI]

AX,2[SI]

1:

DI <del>≪</del> offset

mov

AX~◆bb

mov

AX≪≫user code byte

xchq

AX,ES:[DI]

mov

2[SI], AX

bb ←user code byte

```

and loop

advance to next entry

Note that the user code segment wherein the breakpoints are set is treated as an external data segment in the breakpoint routine, and hence must use a data segment descriptor on a protected mode 286. The user program of course references its code segments through the CS register as executable segments. This means that the debugger needs an alias descriptor for each code segment in the user program that describes the code segment as a data segment. (Note that aliasing of segments requires a certain amount of bookkeeping work in the OS, especially if demand swapping of segments is supported.) The underlying operating system needs to support these data aliases for use by the debugger, but not for use by the user program. This means the debugger either operates at a higher privilege level or in a different task entirely from the user program. The debugger itself, of course is also protected from the program under debug by this same mechanism. In general it may be simpler to develop the debugger as a separate task since then it need not be bound with the user program, it has an entirely separate address and descriptor space, and it may operate at the appropriate privilege level(s) as established by the system. (Note that a debugger within the same task as the faulting or breakpointing program must either be "conforming" or be at the same or higher level of privilege since interrupt-induced level transitions must go to a more privileged (inward) level).

add

loopnz

SI,2

The debugger task needs an entry point for handling breakpoint exceptions. The 'breakpoint occurrence' entry point receives control when the user program executes the breakpoint instruction, INT (implicit #3). It should do the following:

breakpoint occurrence:

The two table lookups above (for CS and IP) may use techniques such as hashing or binary search to speed search time. Once the user is prompted he may do any debugger operation. If or when the user elects to resume execution from the breakpoint, control is transferred back to the user program via the 'current breakpoint' address.

# \* INTERPRETATION TECHNIQUES

Very often interpretation techniques are used to speed the edit-compile-debug cycle, to simplify breakpointing, tracing, single stepping, patching, profiling, etc., and to improve debugger portability. Klint (20) gives an excellent tutorial on interpretation techniques, and the following is adapted to the 286 from his paper.

Four techniques will be given

- i) classical interpreter with opcode table;

- ii) direct threaded code;

- iii) indirect threaded code; and

- iv) partial interpretation via software interrupt.

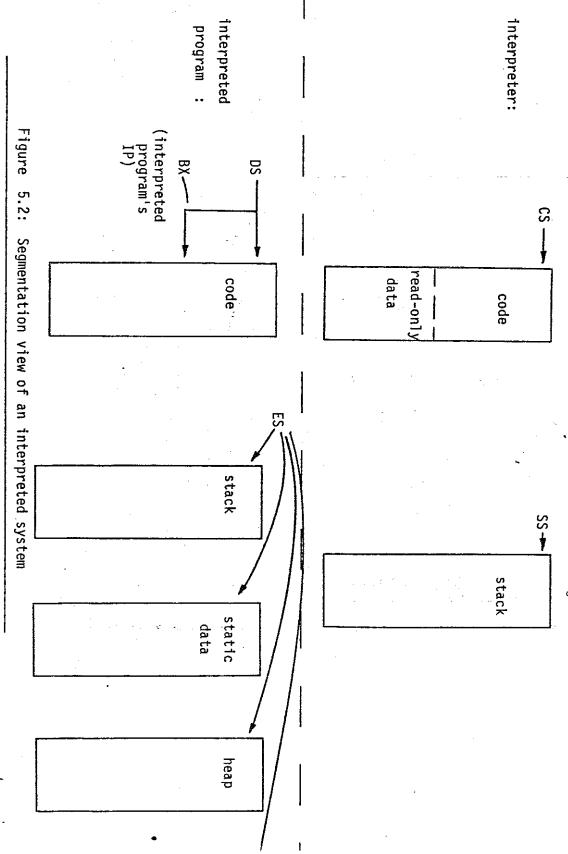

Before describing the techniques, let's first describe the segmentation view of our interpretation schemes. Figure 5.2 shows the various existing segments under an interpreter model. We assume the interpreter is small enough that all its code and read-only data can reside in a single segment (referenced via CS). The interpreter stack uses SS, and scratch data uses the registers or the stack. We assume most read-write data is stored in the interpreted program's data segments, but a small amount of read-write data private to the interpreter could be stored at the base of the stack and be referenced via SS. The user code is the most frequently referenced data for the interpreter, and is referenced via DS, while all types of user data are referenced via ES. This segmentation model is necessary to efficiently utilize the machines four active segment registers. We will use BX as the interpreted program's instruction pointer and maintain it always at the next byte to be read.

Page 5-6

### \* CLASSICAL INTERPRETER

Classic interpretation uses an opcode table (indexed by the opcodes in the interpreted program) to vector to the appropriate interpretation routine:

- pick up user opcode (8-bits, typically) from location DS:[BX];

- increment user PC (BX) appropriately;

- execute routine at location opcode\_table[user opcode].

The interpreter loop is:

| interpret:          | xor<br>movbyte<br>inc<br>jmp | SI,SI<br>SI,[BX]<br>BX<br>opcode_table[SI] | 2<br>2<br>1<br>3-4 | 5<br>2<br>13-15    |