References: CPE380 Single-Cycle Design

The lecture slides as a PDF

provide a good overview of everything with LOTS of Verilog code

showing how everything is done in detail. I don't expect

students to be able to write Verilog implementations like these

from scratch, but I do expect that you can follow the logic, and

at this stage I expect you can handle making minor

modifications. The "complete" single-cycle design presented in

the slides is https://aggregate.org/EE380/onebeq.html.

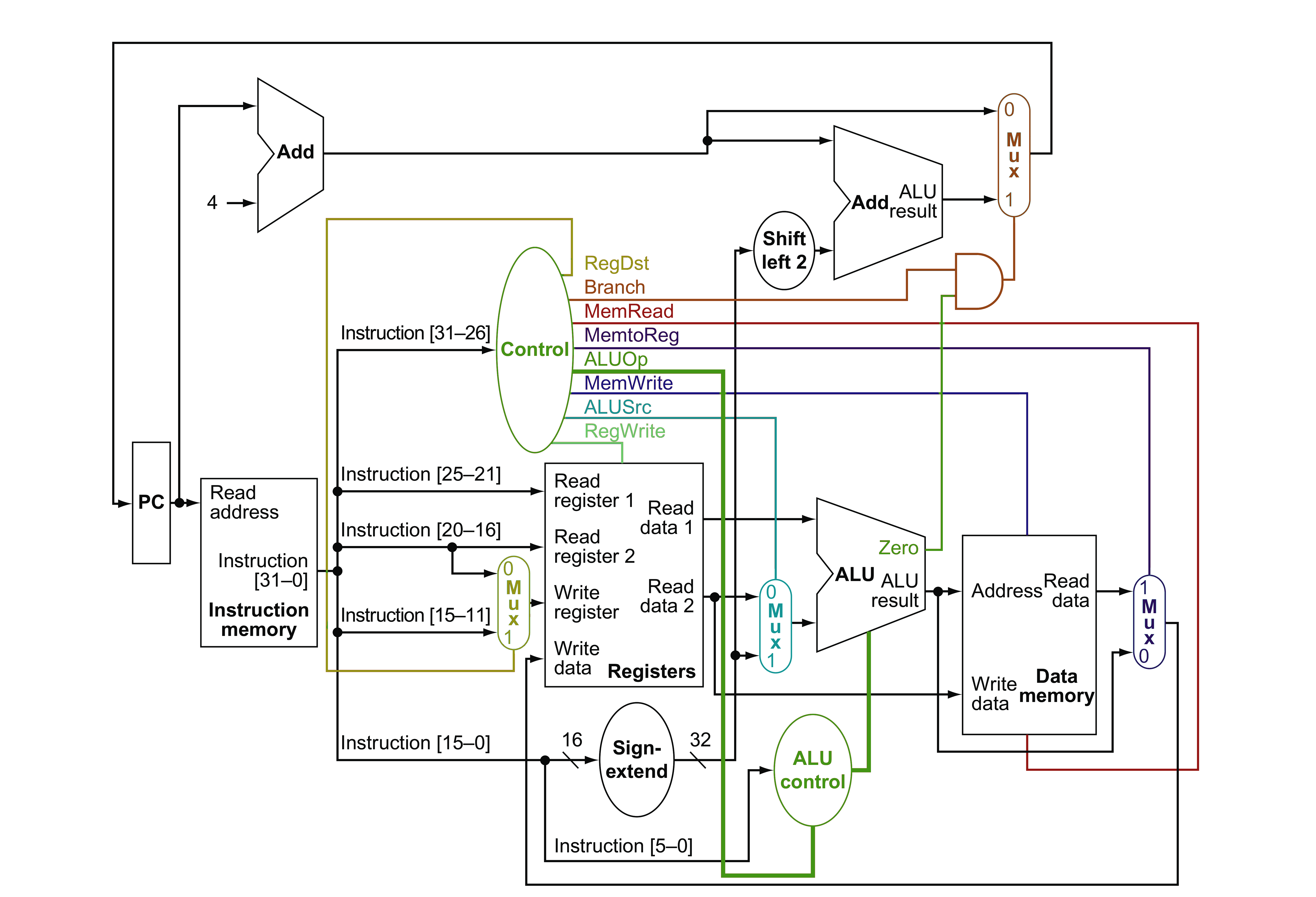

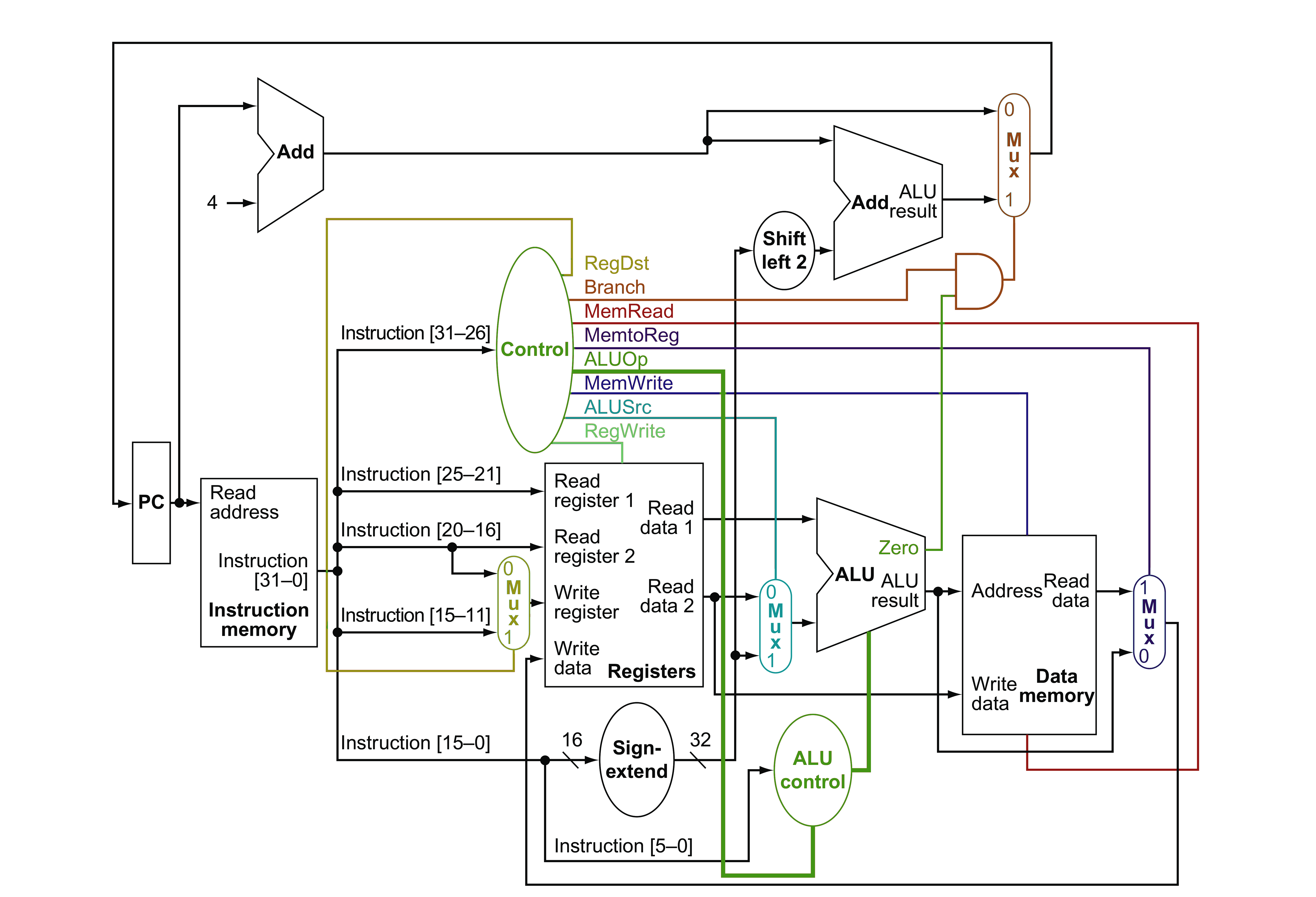

The textbook does have essentially the same single-cycle design

covered, but the description is significantly different, and so

are some control signals. In fact, the design isn't consistent

in various versions of the text and associated materials, with

things like the 0/1 connections for multiplexors varying. Don't

let that bother you -- remember that the design isn't

the important thing here, the process by which you design

is. The tetxbook also doesn't talk about Verilog

implementations....

At this stage, you should be getting comfortable with

reading, understanding, and making minor changes to Verilog

designs. For that, here are some good references:

-

Icarus Verilog (iverilog and vvp)

-

This is the primary free software tool we'll be using for

compiling and simulating Verilog code. It is actually part of

gEDA. Note that

you can install it on Ubuntu Linux systems by simply selecting

it in the Software Center or Synaptic -- it's a standard part of

the Ubuntu distribution, as well as having been ported to

Windows, etc.

-

Icarus Verilog Simulator CGI Interface

-

So that students wouldn't have to deal with installing and

manually running iverilog, vvp, and

covered, Professor Dietz created a WWW browser

interface that allows running them on servers in his lab via a

form interface. This is what's been used for the various Verilog

examples in the lectures, and you can use it for all the Verilog

encountered in this class. There are a few restrictions, mostly

involving the fact that the WWW interface does not allow file

I/O: thus, $dumpfile doesn't take a filename and the

VMEM "files" are read using $readmemh0(...),

$readmemh1(...), etc.

-

EDA playground

-

Here's another WWW interface for running Icarus Verilog... and

various other tools including some commercial simulators.

Requires Log In for use, but registration is free.

-

An Introduction To Verilog (PDF) and Icarus Verilog & Friends (PDF)

-

These are the slides Prof. Dietz prepared for CPE480 overviewing

Verilog as a programming language and how to use free software

tools to develop hardware designs using Verilog.

-

ASIC World

-

This WWW site has a multitude of really nicely prepared

materials showing how to use Verilog. The only catch is that

it very freely mixes different levels all the way down to

transistors... be aware we don't want you doing that here.

-

IEEE Standard for Verilog Hardware Description Language

-

Verilog began as a proprietary HDL around 1983.

Compared to most other hardware design tools at that time,

it is unusual in that it allows specifications to mix

a variety of different levels of hardware abstraction,

even including non-synthesizable programming constructs.

It is now one of the most commonly used HDLs.

Computer Organization and Design.

Computer Organization and Design.