References: CPE380 Pipelined Design

The lecture slides as a PDF

provide a good overview of everything and including a Verilog

implementation showing how things are done in

approximate detail. I don't expect students to be able

to work with the pipelined design in as much detail as I

expected for the single-cycle design; there are way too many

options and interactions.

The book also does a nice job on this... if you have any

doubts, it's a great reference for most of this. I don't expect

you to be able to design a state-of-the-art pipelined

architecture from our quick and somewhat superficial coverage,

but you should have a basic understanding of:

-

Basic pipelining

-

Dividing a single-cycle design into equal-delay stages,

adding buffers between stages

-

Control by moving single-cycle control signals

through the pipe stages along with data

-

Pipeline performance and the concepts associated with pipeline

bubbles (NOP insertion, hardware interlocks)

-

The MIPS pipeline discussed in class and in the text

-

The concepts of VLIW and "superscalar" pipelining --

feeding multiple pipelines simultaneously

-

Structural hazards & how to fix them (e.g., add hardware)

-

Data dependence issues:

-

Read-after-write dependences and value forwarding

-

Write-after-write and write-after-read dependences

and register renaming

-

compile-time code scheduling and

hardware scheduling (out-of-order execution)

-

Control dependence issues:

-

Computation of branch target addresses (from offsets),

delayed branches, and BTBs (Branch Target Buffers)

-

Branch prediction; always not-taken, always taken, always taken

AND not taken, always taken if backward, compiler-marked

instructions for branch-usually-taken or

branch-usually-not-taken, and history schemes (e.g., using a

Branch History Buffer -- BHB) such as the two-bit (four state)

predictor discussed in class

-

The issues involving side-effects for instructions that

were incorrectly executed (incorrectly predicted)

-

The concepts of how to structure a Verilog implementation of a

pipeline, especially the "owner computes" concept

-

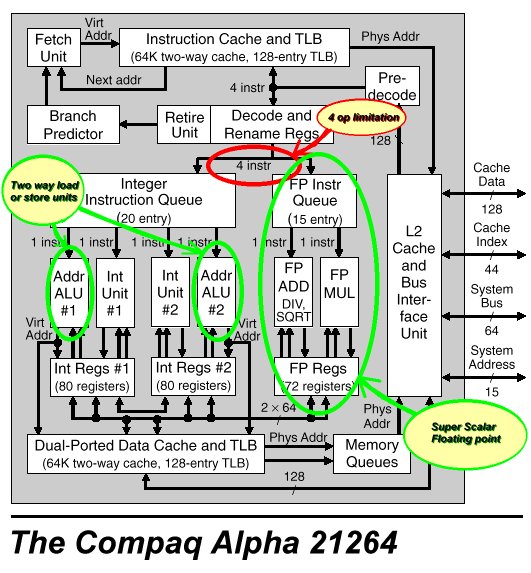

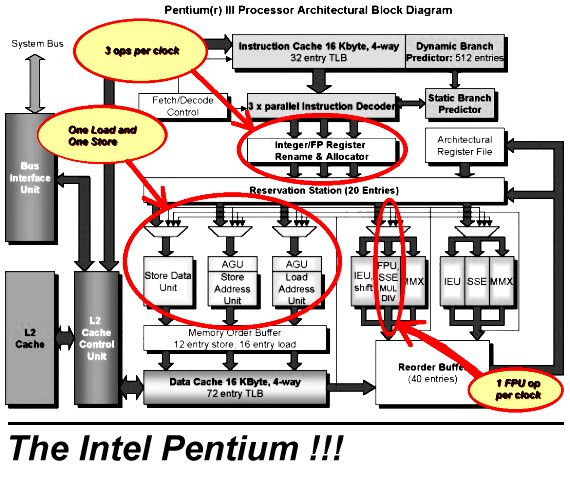

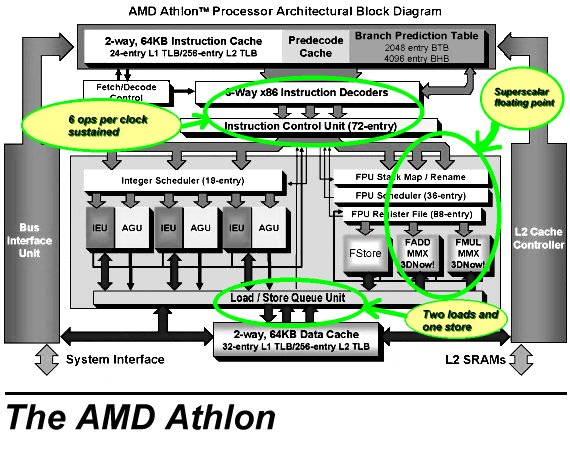

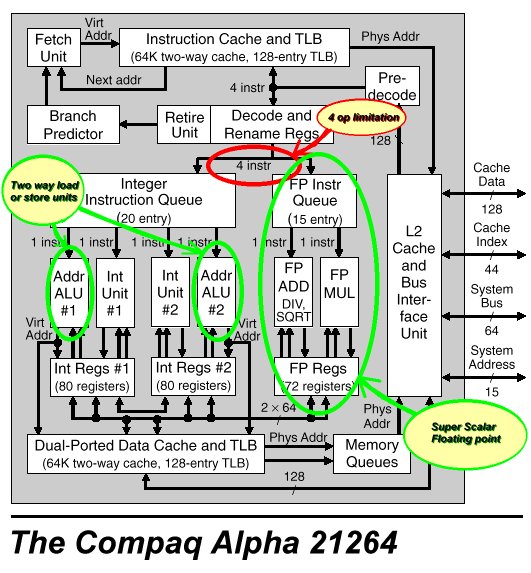

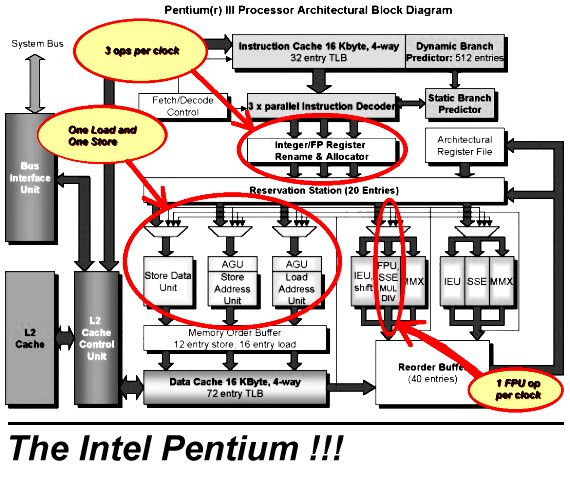

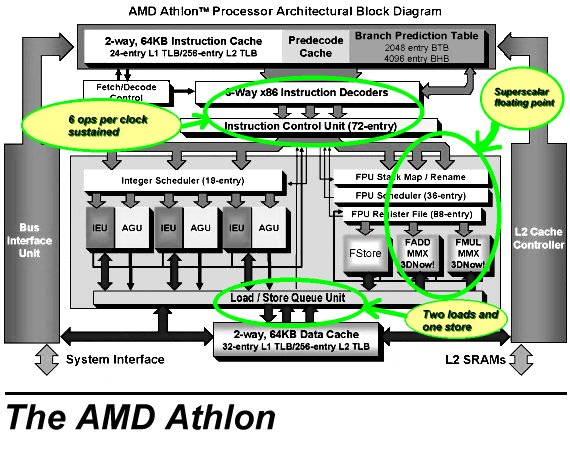

How to make sense of pipeline structures in processor

architecture diagrams like:

Computer Organization and Design.

Computer Organization and Design.