In Assignment 3, you defined the instruction encoding, built an assembler, wrote Verilog code for a pipelined implementation of the Logick instruction set architecture, created a test coverage plan, and tested your design. However, you left out the Log Number System (LNS) instructions. Well, now you're gonna put them in.

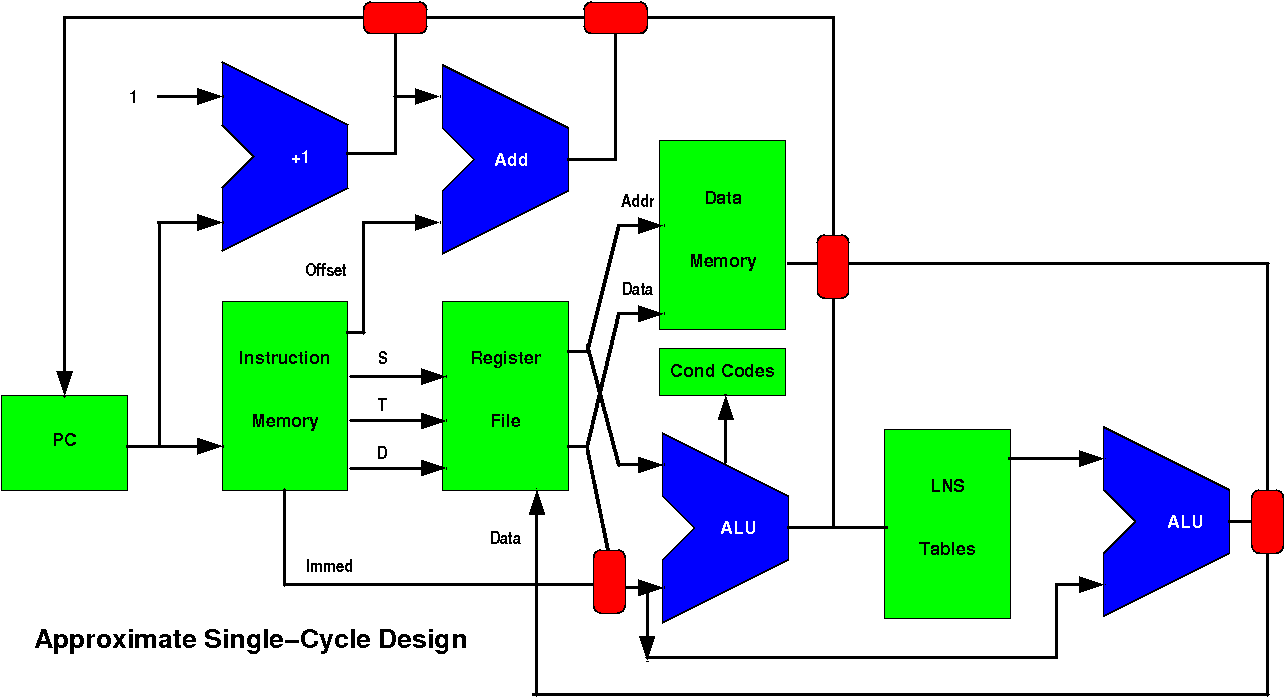

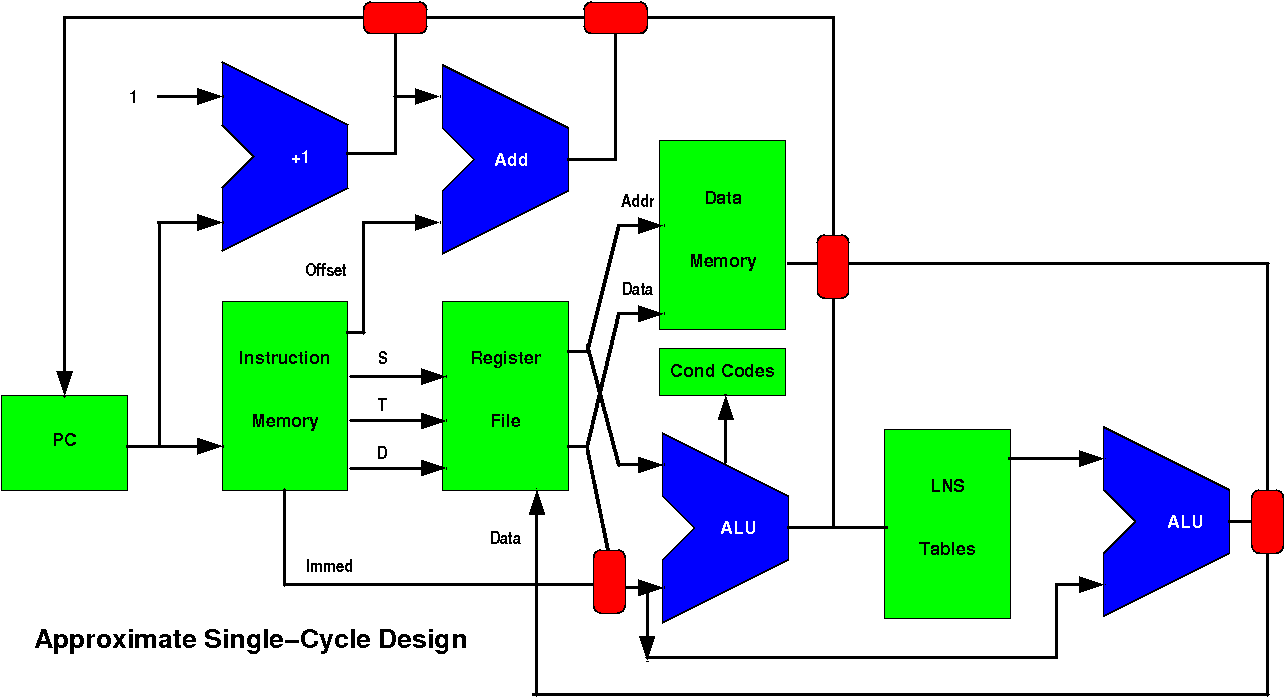

The algorithms for all the LNS operations you need are described in detail at this page on LNS. I can't imagine any reasonable way for you to do this without adding at least two stages to your pipeline, but it's not for my imagination to determine: it's up to you. Here'e a little suggestion for how you might modify the single-cycle starting point for your pipelined design, but it is entirely up to you what form your implementation should take.

Just don't start blindly writing Verilog code... make yourself a single-cycle design, determine how to control it, and then make that into your pipelined implementation.

I've spent a week of class lectures discussing the issues in implementing LNS. There's really not much more to say here.

Assignments 2 and 3 provide an excellent basis for building this design. You may use any of the materials developed by the teams any of your team members were on for those projects. In fact, I strongly recommend you start by creating the best possible implementation of the previous assignment, and then incrementally extend that to support the LNS instructions. Major things to be careful about:

The recommended due date is before class Friday, December 1. Final submissions will be accepted up to just before the final exam begins at 1PM on Monday, December 11, 2017.

Each team will submit a project tarball (i.e., a file with the name ending in .tar or .tgz) that contains all things relevant to your work on the project. Minimally, each project tarball includes the source code for the project and a semi-formal "implementors notes" document as a PDF named notes.pdf. (Fairly obviously, the Implementor's Notes should also say who the implementors are -- list all team members as authors.) It also may include test cases, sample output, a make file, etc., but should not include any files that are built by your Makefile (e.g., no binary executables). For this particular project, name the Verilog source file lnspipe.v.

Submit your tarball below. The file can be either an ordinary .tar file created using tar cvf file.tar yourprojectfiles or a compressed .tgz file file created using tar zcvf file.tgz yourprojectfiles. Be careful about using * as a shorthand in listing yourprojectfiles on the command line, because if the output tar file is listed in the expansion, the result can be an infinite file (which is not ok).

Use the submission form below to submit your project as a single submission for your team -- you do not submit as individuals. The last submission before the final deadline is the one that will be graded.