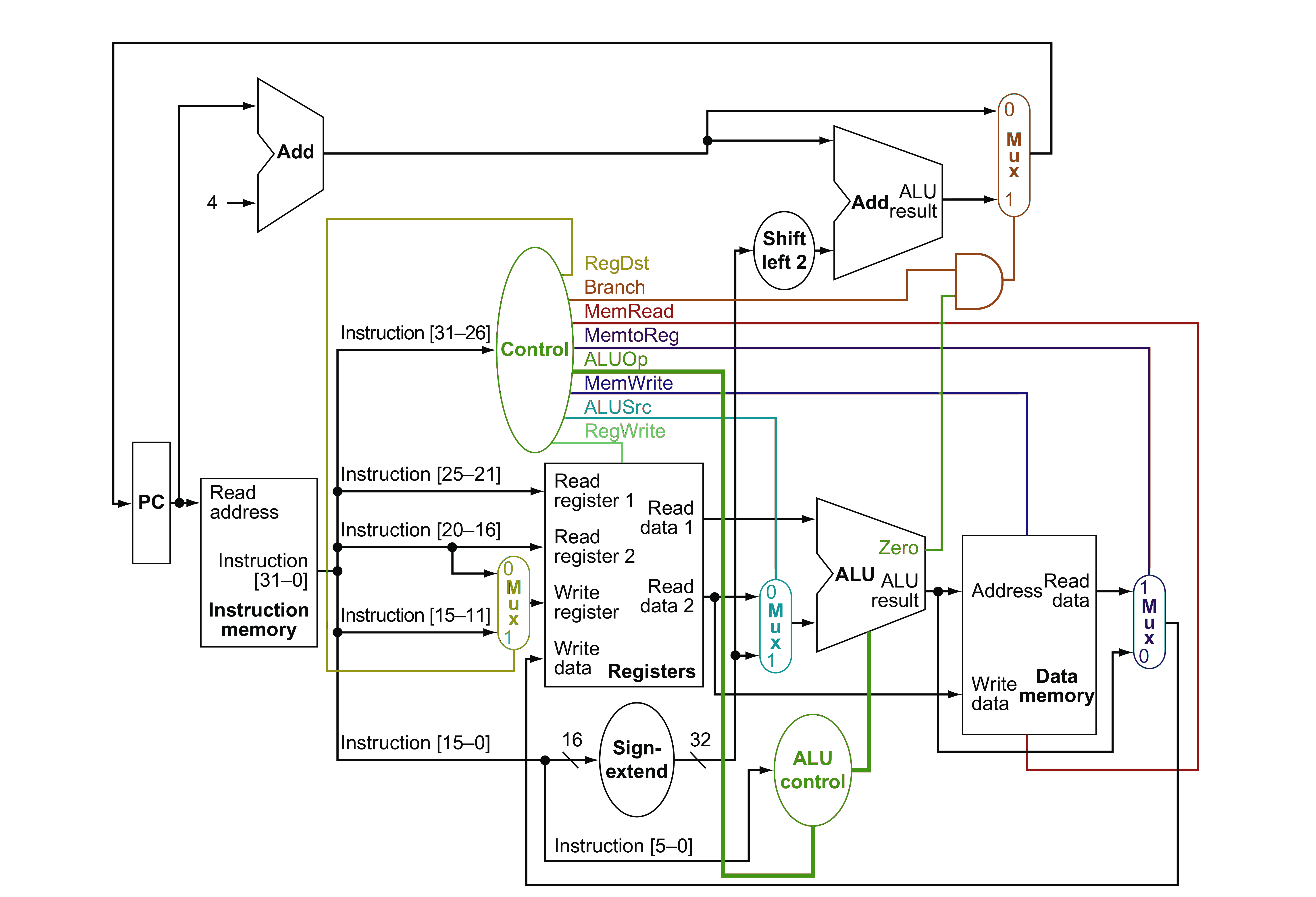

We implemented the single-cycle design shown in the above

(rather large and very familiar) figure as this Verilog code. In order to test the system, various

instructions were placed into memory locations starting at

m[0]. Instead of `RPACK(m[0], 2, 3, 1, 0,

`ADDU), what Verilog code would you write to make the

instruction in m[0] encode a test case for the ldx

$rd,$rt($rs) instruction (opcode `LDX) as

described in the previous question: ldx $3,$2($1)?

Your answer can use one of the macros defined for initializing

instructions, or you can write Verilog code that directly fills

the fields of m[0].